#### 1.0 INTRODUCTION

#### 1.1 DOCUMENT SCOPE

This data sheet applies to both the 3.3 volt or 5.0 volt or 3.3 volt and 5.0 volt (mixed voltage) WD76C20ALV device. The WD76C20ALV can be used with either a 5.0 volt power supply or a low voltage 3.3 volt power supply. Some references are included to the WD76C20A which operates only at 5 volts.

#### 1.2 FEATURES

The WD76C20ALV includes these features:

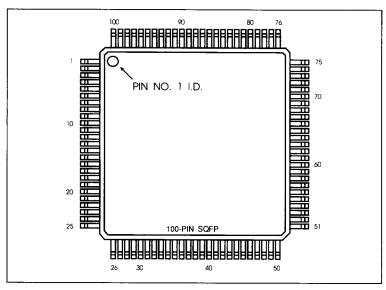

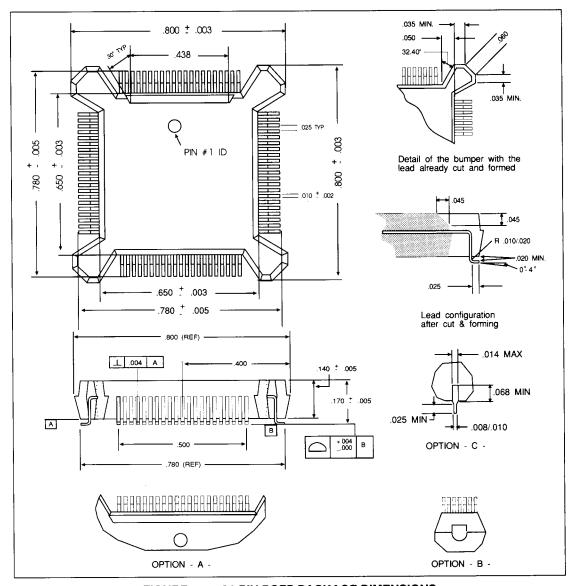

- 84-pin PQFP packages

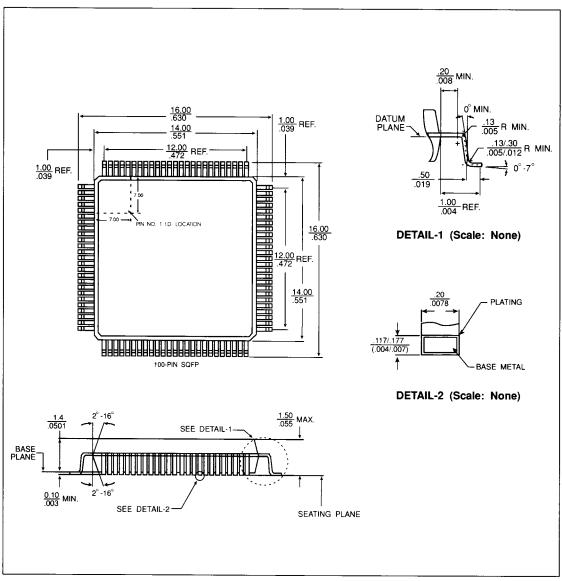

- 100-pin SQFP packages

- 3.3V or 5.0 volt or 3.3 volt and 5.0 volt VCC operation

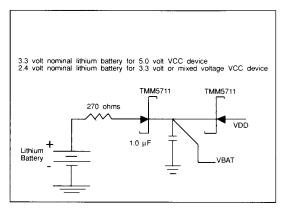

- 3.3V nominal battery backup supply for 5.0V V<sub>CC</sub> device and 2.4V nominal battery backup for 3.3V V<sub>CC</sub> device. The battery backup supply is used for RTC and 114 byte SRAM

- Implemented in a low-power, high-performance, 1.25 micron CMOS technology process

- Option to interface with external analog PLL device (100-pin SQFP only)

- Option to select and de-select digital PLL internal to chip (100-pin SQFP only)

- Default digital PLL, internal to WD76C20ALV device (84-pin PQFP device only)

- Floppy Disk Controller (FDC) software transparent power-down mode with low standby ICC current. FDC features:

- 256 tracks support

- 100% software compatible with NEC 765A

- Integrated high-performance DPLL data separator:

- 125, 250, 300, 500 Kb/sec and 1 Mb/sec data rates

- Option to select 150 Kb/sec FM and 300 Kb/sec MFM data rates only

- Automatic Write Precompensation:

- Defeat option

- Inner track value of 125 or 187 ns pin selectable

- On chip clock generation:

- 2 TTL clock inputs, or

- Single 16 MHz crystal circuit and one TTL clock input

- PQR circuitry- power qualified reset circuitry

- PQR disabled in 3.3 volt application, 84-pin package

- PQR enabled in 5.0 volt application, 84-pin package

- PQREN external pin to enable and disable PQR circuitry internal to chip (only in 100pin SQFP package and 5.0 volt application)

- Host interface read/write accesses compatible with 80286 microprocessors at speeds of 12 MHz with 0 wait states

- Direct floppy disk drive interface no buffers needed

- 48 mA sink output drivers

- Schmitt Trigger input line receivers

- FDC direct PC XT/AT interface compatibility

- Floppy Control and Operations Registers on chip

- In PC/AT mode, provides required signal qualification to DMA channel

- IBM BIOS compatible

- Dual-speed spindle drive support

- PS/2 type drive support

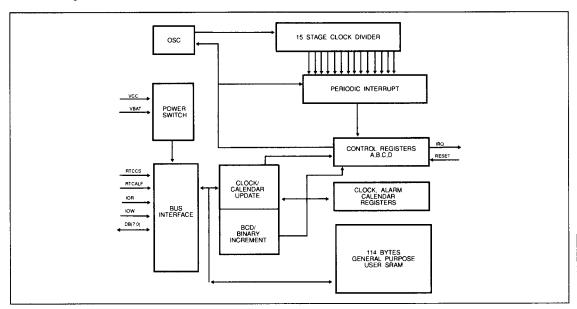

- Real Time Clock (RTC) features:

- Software compatible with Motorola MC146818A.

- Internal time base and oscillator circuitry

- Counts seconds, minutes, and hours

- Counts days of the week, date, month, and year

- Time base input for 32.768 KHz square wave

- Time base oscillator for parallel resonant crystals

- Binary or BCD representation of time, calendar, and alarm

- 12- or 24-hour clock with AM and PM in 12-hour mode

- Daylight savings time option

- Automatic leap year compensation

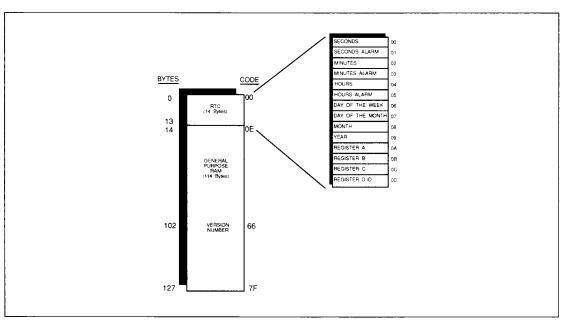

- Interfaced with software as 128 RAM locations

- 114 bytes of general purpose RAM

- Status bit indicates data integrity

- Bus compatible interrupt signals (IRQ)

- Three interrupts are separately software maskable and testable:

- Time-of-day alarm once-per-second to once-per-day

- Periodic interrupt rates from 122 us to 500 ms

- End-of-clock update cycle

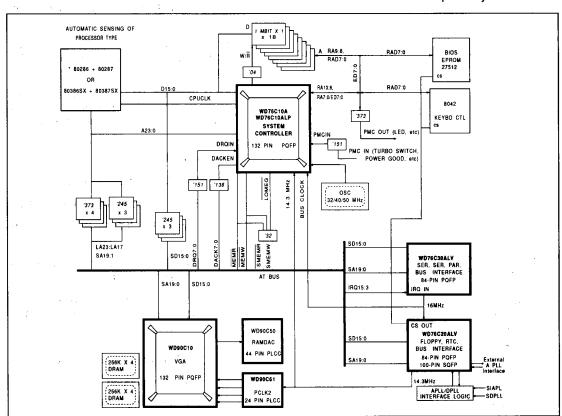

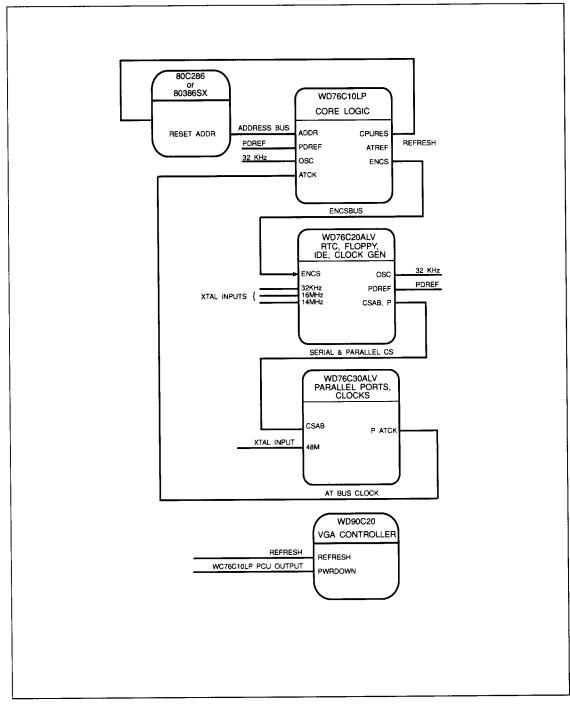

FIGURE 1-1. SYSTEM LEVEL FUNCTIONAL BLOCK DIAGRAM

#### 1.3 GENERAL DESCRIPTION

The WD76C20ALV is a member of the WD7600 chip set which provides a cost-effective, power-efficient solution to PC systems design, especially those relating to "lap-top" devices. The set includes the WD76C10, the WD76C20ALV, and the WD76C30ALV as shown in Figure 1-1. Together these chips provide all necessary logic to build a fully integrated system board for several varieties of IBM PC/AT compatibles including systems using 80286, 80386SX, and 80C286 processors.

As part of this chip set, the WD76C20ALV provides these integral functions:

- Bus Interface Logic

- IDE Interface

- Chip Select Logic

- Floppy Disk Controller

- · Real Time Clock

- Suspend/Resume Logic

The Floppy Disk Controller (FDC) component provides necessary timing and signalling between the host processor peripheral bus and a floppy disk drive through a cable connector.

The Real Time Clock component provides calendar and clock information for the system.

The IDE Interface controls buffering between the system's AT Bus and PC/AT compatible IDE drive interface.

The Bus Interface Logic controls buffering of data between the system's AT Bus and the WD76C20ALV.

The Chip Select Logic section provides decoding for selected chip functions both within the WD76C20ALV and on the PC/AT motherboard.

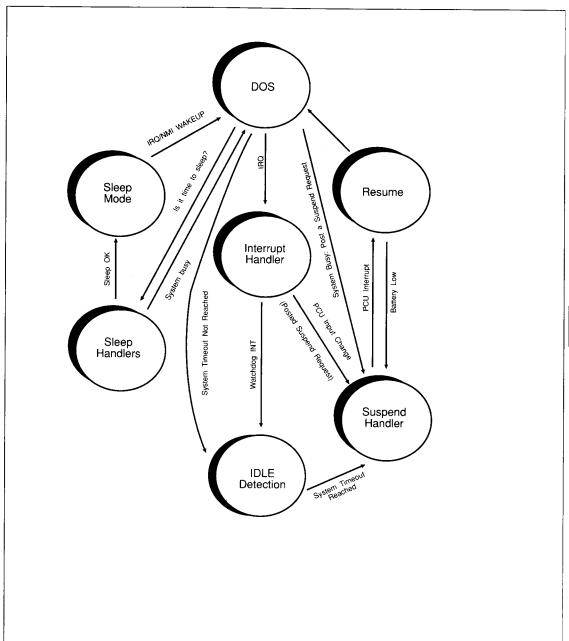

Suspend/Resume Logic provides support for chip set power-down and resume sequences.

The remainder of this manual contains the following information:

**Section 2** discusses the basic system architecture.

Section 3 provides signal descriptions.

**Section 4** discusses the Chip Select Logic in more detail.

Section 5 discusses the Floppy Disk Controller in more detail

Section 6 provides additional information on the IDE Interface.

**Section 7** provides information on the Real Time Clock and SRAM.

**Section 8** gives more information on the Suspend/Resume Logic.

Section 9 provides DC Operating Characteristics.

Section 10 provides AC Interface Timing.

Section 11 shows several package diagrams.

#### 1.4 FEATURE DIFFERENCES BETWEEN WD76C20ALV 84-PIN PQFP AND 100-PIN SQFP PACKAGES

- The WD76C20ALV (84-pin PQFP package) is backward compatible to the WD76C20 device for 5.0 volt and 3.3 volt applications.

- The WD76C20ALV (100-pin SQFP package) has two new programmable chip select outputs, they are PROG2 and PROG3 signals.

- The WD76C20ALV has integrated internal to the chip the level translators for interfacing directly to 5.0 volt or 3.3 volt signals. The WD76C20ALV can operate in 5.0 volt or 3.3 volt or mixed voltage (3.3 volt and 5.0 volt) environment.

- PQR (Power Qualified Reset). The PQR is disabled in 3.3 volt and mixed voltage operation. The PQR can be enabled in 5.0 volt VCC operation for a 100-pin SQFP packaged device by the PQREN pin. Also PQR is enabled as a default in the 5.0 volt, 84-pin PQFP packaged device.

- WD76C20ALV (100-pin SQFP) provides an interface to the external PLL (phase lock loop) device as an option. This is an option and can be selected by SIAPL and SDPLL input signals to the device. See details in the Signal Description section. This feature is provided in the 100-pin SQFP device only.

- The default for the 84-pin PQFP device is digital PLL selection, which is internal to the WD76C20ALV device.

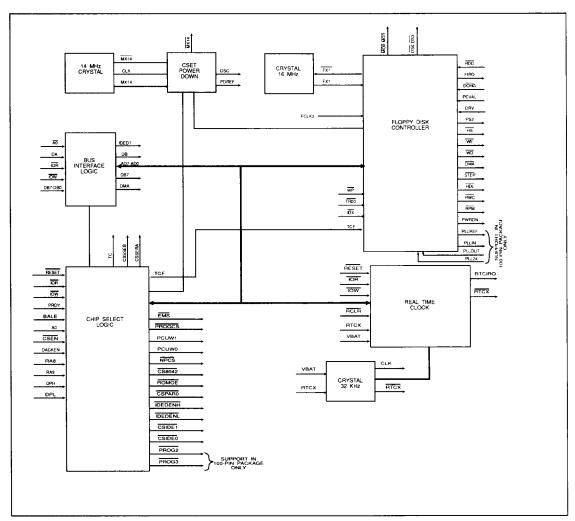

#### 2.0 ARCHITECTURE

The WD76C20ALV has three principal functions as illustrated in Figure 2-1. First, it exchanges control signals with the WD76C10 System Controller. Second, under control of the WD76C10, it exchanges data and qualified operation/status information with the Host via the system's AT Bus. Third, it provides complete control and data read/write services for one to four floppy disk units.

Internally, the WD76C20ALV has the following functional components:

- · Bus Interface Logic

- Chip Select Logic

- IDE Drive Interface

- · Floppy Disk Controller

- · Real Time Clock and associated SRAM

- Suspend/Resume Logic

FIGURE 2-1, WD76C20ALV FUNCTIONAL BLOCK DIAGRAM

These functional components are described briefly in the following sections.

For a more detailed description of Chip Select Logic, IDE Interface Support, Floppy Disk Controller, Real Time Clock, and the Suspend/Resume Logic, refer to Sections 4 through 9. Signals mentioned in the following discussion are listed and described in Section 3.

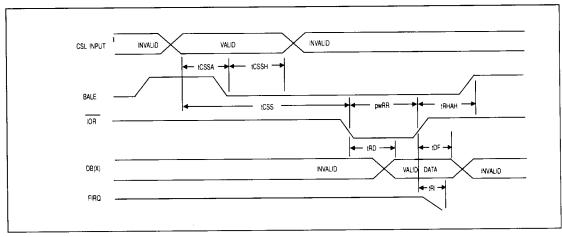

#### 2.1 BUS INTERFACE LOGIC

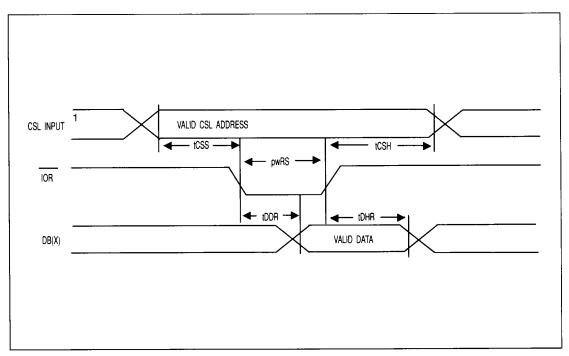

The chip's Bus Interface controls the buffering of bits D0-D7 passing between the system's AT Bus and any WD76C20ALV internal source/destination 8-bit storage cell via the internal bus. The Bus Interface receives the  $\overline{\text{IOR}}$  and  $\overline{\text{IOW}}$  signals from the WD76C10, and with the appropriate chip selects from the Chip Select Logic (CSL), it parallel-passes D0-D7 from the AT Bus to an internal WD76C20ALV cell, or vice versa. The internal cells which the Bus Interface Logic reads/writes to are:

- The Control, Master Status, Status, Data, or Operation Registers in the Floppy Disk Controller

- The 128 registers in the SRAM affiliated with the Real Time Clock.

The Bus Interface Logic also provides a controlled bidirectional path for bit D7 between the AT Bus and the IDE Drive Port.

#### 2.2 CHIP SELECT LOGIC

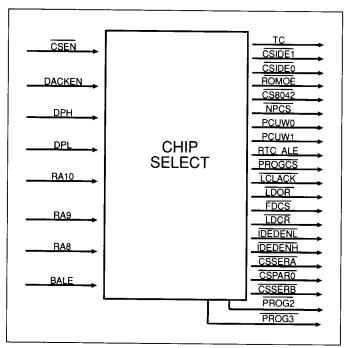

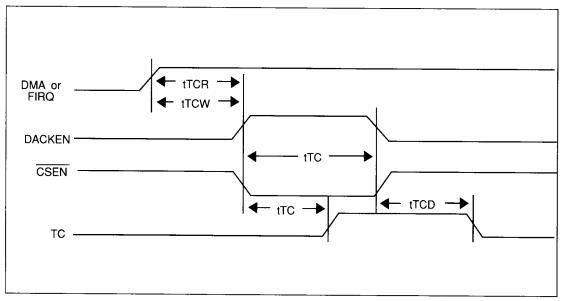

The Chip Select Logic (CSL) component of the WD76C20ALV provides the decoding needed both for selecting chip functions within the WD76C20ALV and on the PC/AT motherboard. It receives the DPL, DPH, and RA8-RA10 signals from the WD76C10 Systems Controller and outputs appropriately decoded chip select signals (detailed in Section 3). Overall control of the decoding processes is accomplished using the CSEN and DACKEN signals from the WD76C10. CSEN enables the decoded output, while DACKEN causes the CSL to ignore the inputs from the WD76C10.

#### 2.3 FLOPPY DISK CONTROLLER

The Floppy Disk Controller (FDC) portion of the WD76C20ALV is a VLSI Super Cell that provides all functions required between the host processor peripheral bus and the cable connector to the floppy disk drive. This provides a comprehensive solution to floppy subsystem control. Among its many features, the FDC possesses a software-transparent power-down mode which facilitates the chip's use in lap-top and portable systems. For more information on this component, see Section 5.

#### 2.4 REAL TIME CLOCK AND SRAM

The Real Time Clock (RTC) component of the WD76C20ALV, in conjunction with the 128-byte register file, provides both calendar (day-of-week, day-of-month, month, and year) and clock (hours, minutes, and seconds) information, along with clocked alarms and a periodic interrupt. This interface gets signals from the WD76C20ALV Bus Interface and Chip Select Logic functions and appropriately buffers bits D0-D7 between the WD76C20ALV internal bus and the RTC internal bus accessing the SRAM.

#### 2.5 SUSPEND/RESUME LOGIC

This functional block is used in conjunction with the RTC time base to provide a 14.318 MHz clock output to the WD76C10. This can switch to a 32.768 KHz clock during the low-power Suspend mode. This logic supports the WD7600 power-down and resume sequencing required to run the Floppy Disk Controller and other components during low power.

# 2.6 DIGITAL/ANALOG PLL (PHASE LOCK LOOP) INTERFACE SUPPORT

Only the WD76C20ALV in the 100-pin SQFP package supports the interface to the external analog PLL device. The interface provided is for the standard external PLL interface as an option.

The default condition for the 84-pin PQFP package is digital PLL selection, which is internal to the WD76C20ALV device. See the table on the next page for details.

| NUMBER | DESCRIPTION                                                                                                            | SIAPL | SDPLL |

|--------|------------------------------------------------------------------------------------------------------------------------|-------|-------|

| 1      | Selects digital PLL internal to the WD76C20ALV device. (84-pin PLCC/PQFP package)                                      | NC    | NC    |

| 2      | Selects digital PLL internal to the WD76C20ALV device. (100-pin SQFP package)                                          | 1     | 1     |

| 3      | Selects internal PLL interface logic to provide interface to analog external analog PLL device. (100-pin SQFP package) | 1     | 0     |

TABLE 2-1. DIGITAL/ANALOG PLL INTERFACE SUPPORT

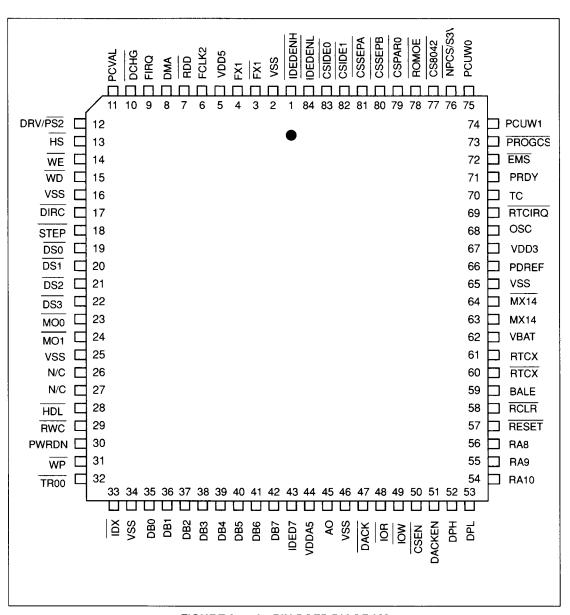

#### 3.0 SIGNAL DESCRIPTION

Figure 3-1 illustrates the signal names and pin locations on the 84-pin PQFP WD76C20ALV package. Figure 3-2 shows the signal locations and

Table 3-1 lists the signal names for the 100-pin SQFP package. Table 3-2 lists the signal names and descriptions grouped by function.

FIGURE 3-1. 84-PIN PQFP DIAGRAM

FIGURE 3-2. 100-PIN SQFP DIAGRAM

| PIN-NAME       | PIN-NAME            | PIN-NAME           | PIN-NAME              |

|----------------|---------------------|--------------------|-----------------------|

| 1-PCUW0        | 26-VDD3             | 51-NC              | 76-NC                 |

| 2-NPCS/S3V     | 27-DRV/PS2          | 52-IDX             | 77- <b>RA</b> 10      |

| 3-CS8042       | 28-HS               | 53-VSS             | 78-RA9                |

| 4-ROMOE        | 29-WE               | 54-DB0             | 79-RA8                |

| 5-CSPAR0       | 30-WD               | 55-DB1             | 80-RESET              |

| 6-CSSERB       | 31-PLLOUT           | 56-DB2             | 81-RCLR               |

| 7-CSSERA       | 32-VSS              | 57-DB3             | 82-BALE               |

| 8-CSIDE1       | 33-DIRC             | 58-DB4             | 83-RTCX               |

| 9-CSIDE0       | 34-STEP             | 59-DB5             | 84-RTCX               |

| 10-IDEDENL     | 35-DS0              | 60-DB6             | 85-VBAT               |

| 11-IDEDENH     | 36-DS1              | 61-DB7             | 86-MX14               |

| 12-PLLREF      | 37-DS2              | 62-IDED7           | 87- <mark>MX14</mark> |

| 13-PLLIN       | 38-DS3              | 63-VDDA5           | 88-VSS                |

| 14- <u>VSS</u> | 39- <del>MO</del> 0 | 64-PROG2           | 89-PQREN              |

| 15-FX1         | 40- <del>MO1</del>  | 65-PROG3           | 90-PDREF              |

| 16-FX1         | 41-VSS              | 66- <b>A</b> 0     | 91-VDD3               |

| 17-VDDD5       | 42-SIAPL            | 67-VSS             | 92-OSC                |

| 18-FCLK2       | 43-SDPLL            | 68-DACK            | 93-RTCIRQ             |

| 19-RDD         | 44-HDL              | 69-ĪOR             | 94-TC                 |

| 20-PLL24       | 45-RWC              | 70- <del>IOW</del> | 95-PRDY               |

| 21-DMA         | 46-PWRDN            | 71-CSEN            | 96-EMS                |

| 22-FIRQ        | 47-WP               | 72-DACKEN          | 97-PROGCS             |

| 23-DCHG        | 48-TR00             | 73-DPH             | 98-PCUW1              |

| 24-PCVAL       | 49-NC               | 74-DPL             | 99-NC                 |

| 25-NC          | 50-NC               | 75-NC              | 100-NC                |

TABLE 3-1. WD76C20ALV PIN ASSIGNMENTS (100 PIN)

| 84-PIN* | 100-PIN** | MNEMONIC     | I/O   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-----------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |           | INTEGRATED L | DRIVE | ELECTRONICS (IDE) INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1       | 11        | IDEDENH      | 0     | IDE Drive Enable High Byte  TTL level output goes active low to enable the IDE drive interface bus transceivers for the high byte of the 16-bit Interface. The signal is used with the CSIDE0 1 card select output signal to the IDE drive only during 16-bit IDE data transfers.                                                                                                                                                                                                                                       |

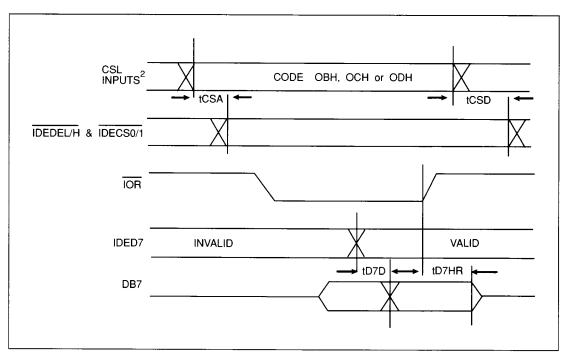

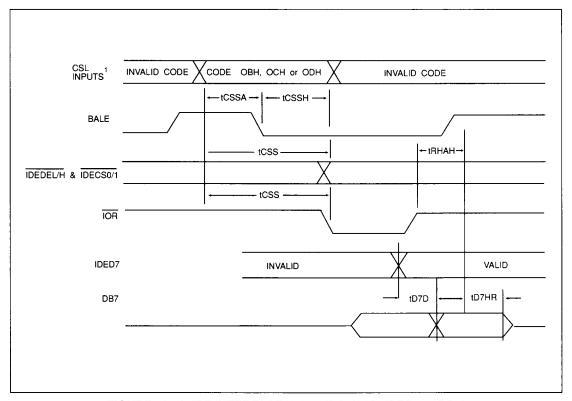

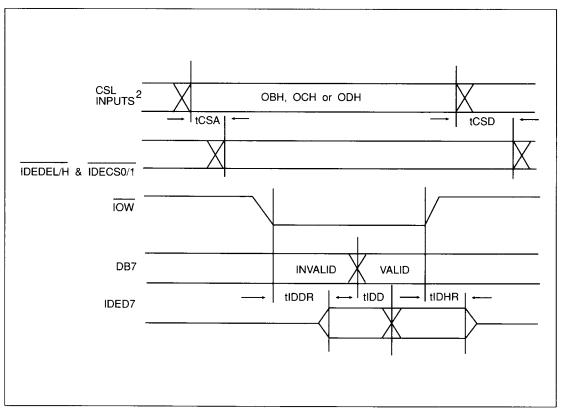

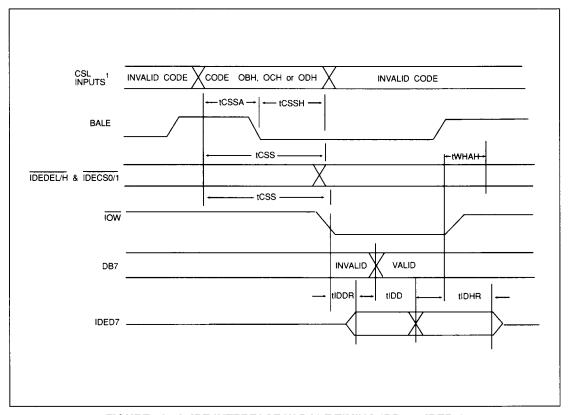

| 43      | 62        | IDED7        | I/O   | IDE Data Bit 7  TTL level I/O providing a data path for bit 7 between the Host and the IDE drive interface. IDED7 is an output, passing data to the IDE drive from DB7 of the Host data bus whenever an IOW to the IDE drive interface is detected. IDED7 is an input, passing data from the IDE drive to DB7 of the Host data bus whenever an IOR of the IDE drive interface is detected, except when reading from address 3F7H. During an IOR of 3F7H, the floppy DCHG status is output on the Host data bus pin DB7. |

| 82      | 8         | CSIDE1       | 0     | IDE Card Select 1 TTL level output is used by the Host to address and communicate with the IDE drive auxiliary registers. Host activates the signal through a decode in the CSL logic block, while at the same time asserting IDEDENL.                                                                                                                                                                                                                                                                                  |

| 83      | 9         | CSIDE0       | 0     | IDE Card Select 0  TTL level output is used by the Host to address and communicate with the IDE drive on the I/O channel. The Host activates the signal through a decode in the CSL logic block, while at the same time asserting IDEDENL or both IDEDENL and IDEDENH.                                                                                                                                                                                                                                                  |

| 84      | 10        | IDEDENL      | 0     | IDE Drive Enable Low Byte  TTL level output goes active low to enable the IDE drive interface bus transceivers for the low byte of the 16-bit Interface. The signal is used with the CSIDE0 and CSIDE1 card select outputs to the IDE drive.                                                                                                                                                                                                                                                                            |

## **TABLE 3-2. SIGNAL DESCRIPTIONS**

NOTE:

\* Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

| 84-PIN* | 100-PIN** | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                                                                                 |

|---------|-----------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |           |          | НО  | OST INTERFACE                                                                                                                                                                                                               |

| 8       | 21        | DMA      | 0   | DMA Request (FDC) In PC AT mode, this pin is tristated, enabled by DMAEN signal from the operations register.                                                                                                               |

| 45      | 66        | A0       | 1   | Address Line 0 Address signal selecting data (=1) or status (=0) information for the FDC. A0=0 during the IOW is illegal except when using user initiated FDC power down mode.                                              |

| 47      | 68        | DACK     | 1   | DMA Acknowledge Used by DMA controller to transfer data from FDC onto the bus. Logical equivalent to FDCS and A0=1. In PC AT mode, this signal is qualified by DMAEN from the operations register.                          |

| 48      | 69        | IOR      | 1   | Input/OutputRead Read enable allowing data or status information to be transferred onto data bus by the WD76C20ALV.                                                                                                         |

| 49      | 70        | ĪŌW      | I   | Input/Output Write Write enable latching data from the bus into WD76C20ALV buffer register.                                                                                                                                 |

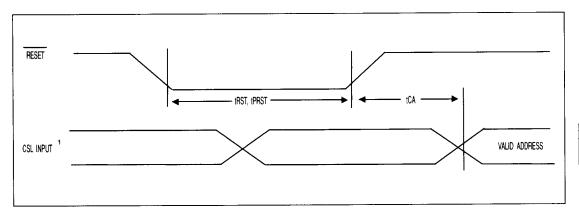

| 57      | 80        | RESET    |     | Reset TTL input resets the WD76C20ALV with the exception of the normal timekeeping operations which will remain uninterrupted. Resets all device outputs. Resets FDC controller, placing microsequencer in idle PC/AT mode. |

<sup>\*</sup> Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

| 84-PIN* | 100-PIN** | MNEMONIC | I/O  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|-----------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |           | FLOPPY   | DISK | CONTROLLER INTERFACE                                                                                                                                                                                                                                                                                                                                                                                         |

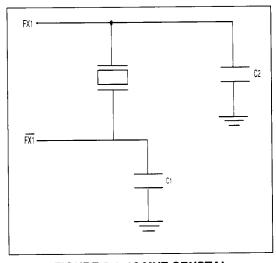

| 3       | 15        | FX1      | 0    | Floppy Crystal Oscillator Output This pin is an oscillator drive output for a 16 MHz parallel resonant crystal. FX1 should be left floating if a TTL level clock is used at pin FX1.                                                                                                                                                                                                                         |

| 4       | 16        | FX1      | l    | Floppy Crystal Oscillator Input A crystal oscillator input requiring a 16 MHz parallel resonant crystal. This oscillator is used for all standard data rates, and may be driven with a 16 TTL level signal instead of using the crystal circuitry.                                                                                                                                                           |

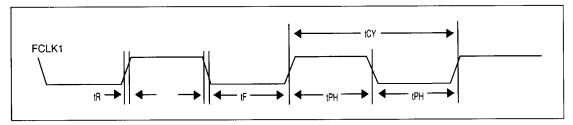

| 6       | 18        | FCLK2    | 1    | Floppy Clock TTL level input used for non-standard data rates, can be driven with a 9.6 MHz clcok for 300kb/s MFM data rate and only be selected from the control register.                                                                                                                                                                                                                                  |

| 7       | 19        | RDD      | I    | FDC Read Disk Data This is the raw serial bit stream from the disk drive. Each falling edge of the pulses represents a flux transition of the encoded data.                                                                                                                                                                                                                                                  |

| 9       | 22        | FIRQ     | 0    | Floppy Interrupt Request Interrupt request indicating completion of command execution or data transfer requests (non-DMA mode). In PC AT mode, this pin is tristated, enabled by the DMAEN signal from the operations register.                                                                                                                                                                              |

| 10      | 23        | DCHG     | I    | FDC Disk Changed This Schmitt Trigger (ST) input senses status from the disk drive indicating active low as the drive door is opened or that the diskette has possibly changed since the last drive selection. The pin has an internal pull-up resistor.                                                                                                                                                     |

| 11      | 24        | PCVAL    |      | Precompensation Value This pin determines the amount of write precompensation used on the inner tracks of the diskette. Logic 1=125 ns, 0=187 ns. In the defeat option, the PCVAL input is a don't care and internally the precompsation value is disabled.                                                                                                                                                  |

| 12      | 27        | DRV/PS2  | I/O  | Drive Set (PS2) In the input mode, a logic 0 indicates to the FDC that a 2-speed spindle motor is present and that FCLK2 should be grounded because it will not be used. As an option this pin can be defined as an output to support the floppy drive connector pin 2 for PS2 style drives, indicating that the FDC is set internally for a single spindle motor. The pin has an internal pull-up resistor. |

NOTE:

\* Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

| 84-PIN* | 100-PIN** | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                |

|---------|-----------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | 28        | HS       | 0   | Head Select This high current driver (HCD) output selects the head, i.e., side, of the floppy disk that is being read or written. Logic 1 = side 0, logic 0 = side 1.                                                                                                                                                                                                      |

| 14      | 29        | WE       | 0   | Write Enable This HCD output becomes true, active low, just prior to writing on the diskette. This allows current to flow through the write head.                                                                                                                                                                                                                          |

| 15      | 30        | WD       | 0   | Write Data This HCD is the write data output. Each falling edge of the encoded data pulse stream causes a flux transition on the media.                                                                                                                                                                                                                                    |

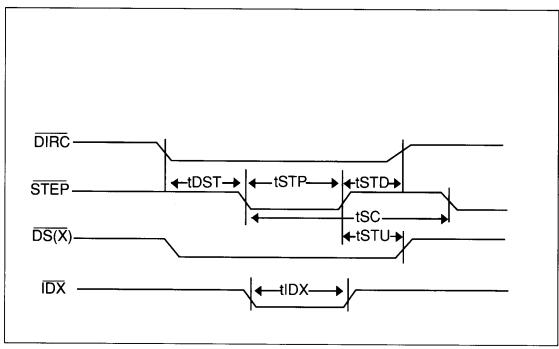

| 17      | 33        | DIRC     | 0   | Direction (Stepper) This HCD output determines the direction of head stepper motor. Logic 1 = outward motion, logic 0 =inward motion.                                                                                                                                                                                                                                      |

| 18      | 34        | STEP     | 0   | Stepper This HCD output issues an active low pulse for each track to track movement of the head.                                                                                                                                                                                                                                                                           |

| 29      | 45        | RWC/RPM  | 0   | Reduced Write Current or RPM Select This HCD output, when active low, causes a reduced write current when bit density is increased toward the inner tracks, becoming active when tracks greater than 28 are accessed. In PC/AT mode, this signal can be used on 2-speed drives to select 300 RPM, active low, when 250 MFM or 125 FM Kb/s data rate is selected and DRV=0. |

| 30      | 46        | PWRDN    | 0   | Power Down TTL compatible output when active high indicates that the FDC portion of the WD76C20ALV has gone into powerdown mode. This signal can be used to power-down the floppy drive if supported.                                                                                                                                                                      |

| 31      | 47        | WP       | I   | Write Protect This Schmitt Trigger (ST) input senses status from the disk drive indicating, active low, when a diskette is write protected.                                                                                                                                                                                                                                |

| 32      | 48        | TR00     | I   | Track 00 This ST input senses status from the drive indicating, active low, when the head is positioned over the outermost track, track 00.                                                                                                                                                                                                                                |

| 33      | 52        | IDX      |     | Index This ST input senses status from the drive indicating, active low, when the head is positioned over the beginning of a track, marked by an index hole.                                                                                                                                                                                                               |

NOTE:

\* Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

| 84-PIN* | 100-PIN** | MNEMONIC | I/O             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-----------|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |           | (        | ELECT INTERFACE |                                                                                                                                                                                                                                                                                                                                                                                                            |

| 50      | 71        | CSEN     | 1               | Chip Select Enable The chip select enable TTL input line is used to output enable the appropriate CSL control line as decoded from the RA8, RA9, RA10, DPL, and DPH inputs. When DACKEN is asserted low, the function of CSEN is negated. When used to enable and disable the WD76C30ALV 48 MHz clock, CSEN acts as a strobe to a latch. When it and DACKEN are both asserted, the TC output will go high. |

| 51      | 72        | DACKEN   | I               | DMA Acknowledge Enable TTL input that indicates the Host is performing a DMA transfer unrelated to the WD76C20ALV. When active low, it is used to disqualify all CSL input lines.                                                                                                                                                                                                                          |

| 52      | 73        | DPH      | I               | Chip Select Address Parity High Decoded chip select TTL input, bit CS4.                                                                                                                                                                                                                                                                                                                                    |

| 53      | 74        | DPL      | ł               | Chip Select Address Parity Low Decoded chip select TTL input, bit CS3.                                                                                                                                                                                                                                                                                                                                     |

| 54      | 77        | RA10     | ı               | Chip Select Address Line 10 Decoded chip select TTL input, bit CS2.                                                                                                                                                                                                                                                                                                                                        |

| 55      | 78        | RA9      | ı               | Chip Select Address Line 9 Decoded chip select TTL input, bit CS1.                                                                                                                                                                                                                                                                                                                                         |

| 56      | 79        | RA8      | 1               | Chip Select Address Line 8 Decoded chip select TTL input, bit CS0.                                                                                                                                                                                                                                                                                                                                         |

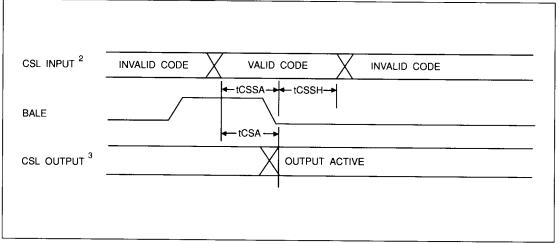

| 59      | 82        | BALE     | I               | Chip Select Bus ALE TTL input when active high, causes latches on the CLS input lines (CSEN, RA8, RA9, RA10, DPL, and DPH) to become transparent. When BALE is forced low, the data in the transparent latches is latched. This pin has an internal pull-up resistor so the pin can be left unconnected and the latches are transparent.                                                                   |

| 70      | 94        | ТС       | 0               | Terminal Count  TTL level output used to indicate that the final count has been reached during a Host DMA transfer unrelated to the WD76C20ALV. It is also used internally by the FDC to indicate that a DMA transfer to the floppy drive is complete. TC asserts high when both DACKEN and CSEN are asserted. (DACKEN=1, CSEN=0)                                                                          |

<sup>\*</sup> Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

| 84-PIN* | 100-PIN** | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                              |

|---------|-----------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71      | 95        | PRDY     | I   | Processor Ready Schmitt Trigger input senses processor ready status to help latch the CSL inputs correctly during system byte swapping activities. This pin has an internal pull-up resistor so that it can be left unconnected when not used. The PRDY input should be used in system designs that use the BALE pin.                                                    |

| 72      | 96        | EMS      | 0   | External EMS TTL card select output decoded from CSL input lines and issued to select external EMS.                                                                                                                                                                                                                                                                      |

| 73      | 97        | PROGCS   | 0   | CMOS Chip Select Program Chip CMOS chip select output decoded from CSL input select lines and issued as a programmable chip select.                                                                                                                                                                                                                                      |

| NA      | 64        | PROG2    | 0   | CMOS Chip Select Program Chip<br>CMOS chip select output decoded from CSL input select<br>lines and issued as a programmable chip select 2.                                                                                                                                                                                                                              |

| NA      | 65        | PROG3    | 0   | CMOS Chip Select Program Chip<br>CMOS chip select output decoded from CSL input select<br>lines and issued as a programmable chip select 3.                                                                                                                                                                                                                              |

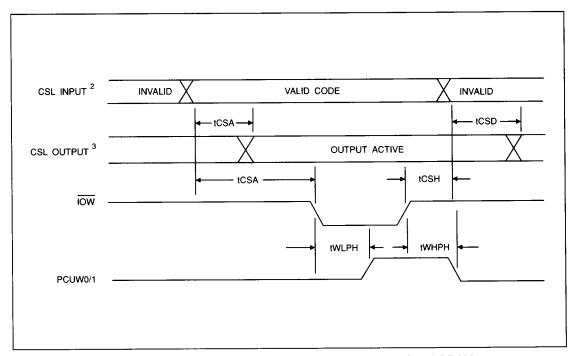

| 74      | 98        | PCUW1    | 0   | Power Control Unit Write Strobe 1 TTL write strobe output decoded from CSL input lines and issued to write to the PCU #1.                                                                                                                                                                                                                                                |

| 75      | 1         | PCUW0    | 0   | Power Control Unit Write Strobe 0 TTL write strobe output decoded from CSL input lines and issued to write to the PCU #0.                                                                                                                                                                                                                                                |

| 76      | 2         | NPCS     | 0   | Numerical Processor Chip Select TTL chip select output decoded from CSL input lines and issued to select the numerical processor, the 80287.                                                                                                                                                                                                                             |

|         |           | S3V      | 1   | Sense 3.3V or 5.0V VCC Operation This signal is used to latch the information on this pin during system reset or power-up reset. Internally all input buffers are configured to accept TTL levels for 3.3 volt or 5.0 volt VCC operation. (VCC=VDD3) When S3V=0, the input threshold is set for 3.3 volt VCC.† When S3V=1, the input threshold is set for 5.0 volt VCC.† |

| 77      | 3         | CS8042   | 0   | 8042 Chip Select TTL chip select output decoded from CSL input lines and issued to select the 8042.                                                                                                                                                                                                                                                                      |

| 78      | 4         | ROMOE    | 0   | ROM Output Enable TTL chip select output decoded from CSL input lines and issued to output enable the BIOS ROM.                                                                                                                                                                                                                                                          |

<sup>\*</sup> Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

† The VCC here denotes VDD3 power pin. All input receivers are powered by a VDD3 power pin.

| 84-PIN* | 100-PIN** | MNEMONIC | I/O    | DESCRIPTION                                                                                                                                                                                                                                                                                   |

|---------|-----------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 79      | 5         | CSPAR0   | 0      | CSL Parallel Port#0 Chip Select TTL chip select output decoded from CSL input lines and issued as a chip select to the WD76C30ALV to enable the parallel port #0.                                                                                                                             |

| 80      | 6         | CSSERB   | 0      | CSL Serial Port B Chip Select TTL chip select output decoded from CSL input lines and issued as a chip select to the WD76C30ALV to enable the serial port B.                                                                                                                                  |

| 81      | 7         | CSSERA   | 0      | CSL Serial Port A Chip Select TTL chip select output decoded from CSL input lines and issued as a chip select to the WD76C30ALV to enable the serial port A.                                                                                                                                  |

|         |           | REA      | AL TIM | E CLOCK INTERFACE                                                                                                                                                                                                                                                                             |

| 58      | 81        | RCLR     | 1      | Real Time Clock RAM Clear TTL input used to clear all 114 bytes of the general purpose RAM. None of the clock, calendar, or RAM functions are interrupted, and the 14 registers that are used by the RTC are left unchanged. This pin has an internal pull-up so it must be left unconnected. |

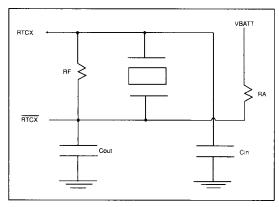

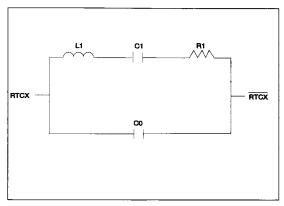

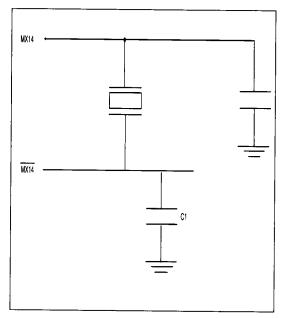

| 60      | 83        | RTCX     | 0      | Real Time Clock Time Base XTAL Out Crystal oscillator output for parallel resonant AT cut crystal at 32.768 KHz.                                                                                                                                                                              |

| 61      | 84        | RTCX     | ł      | Real Time Clock Time Base XTAL In<br>Crystal oscillator input (32.768 KHz) for use with crystal<br>oscillator circuit.                                                                                                                                                                        |

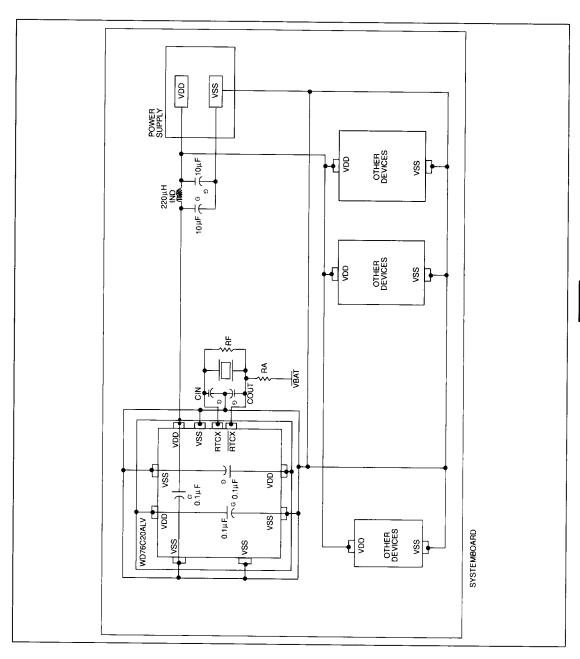

| 62      | 85        | VBAT     | NA     | Battery Backup Battery backup power supply V <sub>DD</sub> pin. A 3.3/2.0-volt battery connector can be attached here to maintain the RTC timekeeping functions and SRAM integrity during system power downs. The 3.3/2.0-volt based on the 5.0/3.3-volt systems respectively.                |

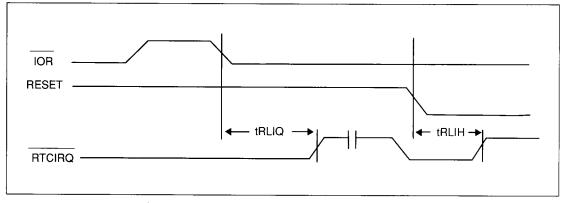

| 69      | 93        | RTCIRQ   | 0      | Real Time Clock Interrupt Request TTL output that is set to tristate unless the RTC needs to interrupt the processor, during which time the pin goes low and stays low until register C is read, or the part is reset through the RESET pin.                                                  |

NOTE:

\* Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

| 84-PIN* | 100-PIN** | MNEMONIC | I/O    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-----------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |           | SUSPENI  | D /RES | SUME SUPPORT INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 63      | 86        | 14MX     | ı      | 14 MHz Crystal Oscillator Input Crystal oscillator input for the 14.318 MHz oscillator.                                                                                                                                                                                                                                                                                                                                                                                 |

| 64      | 87        | 14MX     | 0      | 14 MHz Crystal Oscillator Output Crystal oscillator output for the 14.318 MHz oscillator.                                                                                                                                                                                                                                                                                                                                                                               |

| 66      | 90        | PDREF    | 0      | Power Down Refresh External DRAM refresh line used to support the WD76C10 when the WD76C10 goes into hibernation mode. During hibernation mode, this signal provides a 1.0 $\mu$ s $\pm$ 5 $\mu$ s pulse once every 122.1 $\mu$ s (using a 50% duty cycle), and is used to maintain the DRAM integrity with as little power as possible. Hibernation mode is entered when a CSL address of 15H is detected, and hibernation mode is exited when a CSL of 16H is issued. |

| 68      | 92        | OSC      | 0      | Oscillator (WD76C10 Clock Driver) TTL clock driver output used to support the WD76C10. When not in the WD76C10's "hibernation" mode, the output waveform is a 14.318 MHz square wave, and when in hibernation mode it becomes a 32.768 KHz square wave. The WD76C10 hibernation mode is entered when a CSL address of 15H is detected, and hibernation mode is exited when a CSL address of 16H is issued.                                                              |

|         |           |          |        | DATA BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 35-42   | 54-61     | DB(0:7)  | I/O    | Data/Address Bus 8-bit bi-directional, tristateable data bus.                                                                                                                                                                                                                                                                                                                                                                                                           |

TABLE 3-2. SIGNAL DESCRIPTIONS (CONTINUED)

NOTE:

\* Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

| 84-PIN* | 100-PIN** | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|-----------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |           |          | МО  | TOR CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23      | 39        | MO0      | 0   | Motor On #0 This HCD output, when active low, is motor on enable bit 0. The proper motor enable signal can be decoded externally if required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 24      | 40        | MO1      | 0   | Motor On #1 This HCD output, when active low, is motor on enable bit 1. The proper motor enable signal can be decoded externally if required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 26      | 42        | SIAPL    | I   | Select Analog PLL Device This input signal is used to select the analog PLL interface logic internal to the WD76C20ALV device as an option in the 100-pin SQFP package. This signal is used in conjunction with the SDPLL input signal. See detailed description of options in section 2.6. This feature is only supported in the 100-pin SQFP package.  SIAPL=1 selects the internal analog PLL interface logic for the external PLL device.  SIAPL=1 selects the internal digital PLL logic and disables the external analog PLL interface. It has an internal pull-up and can be a no connect in the 84-pin PQFP device. |

| 27      | 43        | SDPLL    |     | Select Digital PLL Logic This input signal is used to select the digital PLL internal to the WD76C20ALV device. This input signal in conjunction with SIAPL determines the option of DPLL or APLL selection. See detailed description in section 2.6. SDPLL=1 selects DPLL. SDPLL=0 selects the internal analog PLL interface for the external PLL device This feature is only supported in the 100-pin SQFP package. The default for the 84-pin PQFP is digital PLL selection. This signal has an internal pull-up and can be a no connect in the 84-pin PQFP device.                                                      |

#### NOTE:

<sup>\*</sup> Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

| 84-PIN* | 100-PIN** | MNEMONIC   | I/O  | DESCRIPTION                                                                                                                                                                        |

|---------|-----------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |           |            | D    | RIVE SELECT                                                                                                                                                                        |

| 19      | 35        | DS0        | 0    | Drive Select #0 This HCD output, when active low, is Drive #0 select in PC/AT mode, enabling the interface in the disk drive. The signal is qualified by the MOEN0 signal.         |

| 20      | 36        | DS1        | 0    | Drive Select #1 This HCD output, when active low, is Drive #1 select in PC/AT mode, enabling the interface in the disk drive. The signal is qualified by the decoded MOEN1 signal. |

| 21      | 37        | DS2        | 0    | Drive Select #2 This HCD output, when active low, is Drive #2 select in PC/AT mode, enabling the interface in the disk drive. The signal is qualified by the decoded MOEN2 signal. |

| 22      | 38        | DS3        | 0    | Drive Select #3 This HCD output, when active low, is Drive #3 select in PC/AT mode, enabling the interface in the disk drive. The signal is qualified by the decoded MOEN3 signal. |

| 28      | 44        | HDL        | 0    | Head Load This HCD output when active low causes the Head to be loaded against the media in the selected drive.                                                                    |

|         |           | EXTERNAL A | NALO | G PLL INTERFACE (OPTIONAL)                                                                                                                                                         |

| NA      | 12        | PLLREF     | 0    | Phase Lock Loop Ref<br>Interface to external PLL signal input.                                                                                                                     |

| NA      | 13        | PLLIN      | 0    | Phase Lock Loop In Interface to external PLL comparator input.                                                                                                                     |

| NA      | 20        | PLL24      | I    | Phase Lock Loop Clock This is the 24 MHz clock input. Tie to ground if not used.                                                                                                   |

| NA      | 31        | PLLOUT     | I    | Phase Lock Loop Out VCO output from the external PLL to the WD76C20ALV PLL interface logic. Tie to ground if not used.                                                             |

|         |           | F          | POWE | R QUALIFY RESET                                                                                                                                                                    |

| NA      | 89        | PQREN      | I    | Power Qualifed Reset This input when active high enables the floppy disk controller internal power-up reset circuitry. This applies only to 5.0 volt applications.                 |

NOTE:

\* Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

| 84-PIN*                 | 100-PIN**                             | MNEMONIC | I/O    | DESCRIPTION                                                                     |

|-------------------------|---------------------------------------|----------|--------|---------------------------------------------------------------------------------|

|                         |                                       | POWE     | R, GRO | DUND, MISCELLANEOUS                                                             |

| 67                      | 26, 91                                | VDD3     | NA     | 3.3V Power or 5.0 V Power Power to device core and I/O                          |

| 44                      | 63                                    | VDDA5    | NA     | +5V Power or 3.3 V Power 5 volt or 3.3 volt power for AT bus interface          |

| 5                       | 17                                    | VDDD5    | NA     | <b>+5V Power or 3.3 V Power</b><br>5 volt or 3.3 volt power for drive interface |

| 2, 16, 25<br>34, 46, 65 | 5, 14, 32, 41,<br>53, 67, 88          | VSS      | NA     | Ground                                                                          |

| NA                      | 25, 49, 50,<br>51, 75, 76,<br>99, 100 |          | NA     | Not Connected and Not Defined                                                   |

#### NOTE:

<sup>\*</sup> Pin numbers are for the 84-pin package

\*\* Pin numbers are for the 100-pin package

# 7

# 3.1 MAPPING OF POWER PINS TO I/O SIGNALS AND DEVICE CORE

This section summarizes the mapping of device signal pins to a particular power pin connected to a 3.3 volt or 5.0 volt board power plannar.

There are three VDD pins in the WD76C20ALV device. Table 3-3 shows one of the mixed mode power pin distribution examples for mapping the power pins to the signals. The VDD pin description and pin numbers for 84-pin PQFP and 100-pin SQFP packages are included.

Table 3-4 shows the group of signals associated with a particular VDD power pin.

| POWER PIN NAME | DESCRIPTION        | 84-PIN PQFP# | 100-PIN SQFP# |

|----------------|--------------------|--------------|---------------|

| VDD3           | 3.3 volt power pin | 67           | 26, 91        |

| VDDA5          | 5.0 volt power pin | 44           | 63            |

| VDDD5          | 5.0 volt power pin | 5            | 17            |

TABLE 3-3. EXAMPLE MAPPING OF I/O POWER PINS TO SIGNALS

Note: VDDA5 can be connected to either 5.0 volts or 3.3 volts VDDD5 can be connected to either 5.0 volts or 3.3 volts VDD3 can be connected to either 5.0 volts or 3.3 volts All the input receivers are powered by VDD3 power pin

The device can be powered by all 5.0 volt VDDs or 3.3 volt VDDs or 5.0 volt and 3.3 volt mixed mode VDDs as long as the device interface requirements are met.

| GROUP# | DESCRIPTION              | SIGNAL NAMES                                                                                  | BUFFER<br>TYPE | VDD<br>TYPE                  |

|--------|--------------------------|-----------------------------------------------------------------------------------------------|----------------|------------------------------|

|        | GROUP 1, VDD3: 5.0 VC    | OLT OR 3.3 VOLT DEVICE CORE AN                                                                | ID I/O         |                              |

| <br>1  | Chip core and            | chip core                                                                                     | N/A            | VDD3                         |

|        | IDE Interface            | IDEDENH, IDEDENL                                                                              | 0              | VDD3                         |

|        | FDC Interface            | FX1<br>FX1, DCHG, PCVAL,<br>WP, TR00, IDX, RDD, FCLK2                                         | 0              | VDD3<br>VDD3*<br>VDD3*       |

|        |                          | DRV/PS2                                                                                       | I/O (OC)       | VDD3*                        |

|        |                          | HS, WE, WD, DIRC, STEP, HDL<br>RWC/RPM, MO0-1, DS(0-3)                                        | OC<br>OC       | VDD3*<br>VDD3*               |

|        |                          | PWRDN<br>PQREN, SIAPL, S3V, SDPLL                                                             | 0              | VDD3<br>VDD3                 |

|        | AT Interface             | RESET                                                                                         |                | VDD3                         |

|        | Chip Select Interface    | CSEN, DACKEN, DPH, DPL,<br>RA8, RA9, RA10, PRDY                                               | 1              | VDD3<br>VDD3                 |

|        |                          | EMS, PROG2, PROG3,<br>PROGCS, PCUW1, PCUW0,<br>NPCS, ROMOE, CS8042,<br>CSPARO, CSSERB, CSSERA | 0 0 0          | VDD3<br>VDD3<br>VDD3<br>VDD3 |

|        | RTC Interface            | RCLR, RTCX<br>RTCIRQ, RTCX                                                                    | 0              | VDD3<br>VDD3                 |

|        | Suspend/Resume Interface | MX14<br>MX14, PDREF                                                                           | 0              | VDD3                         |

| -      | GROUP 2, VDDD5: 5.       | 0 VOLT OR 3.3 VOLT DRIVE INTERI                                                               | FACE           |                              |

| 2      | IDE Interface            | CSIDE1, CSIDE0 * IDED7                                                                        | 0 1/0          | VDDD5<br>VDDD5               |

|        | GROUP 3, VDDA5: 5.0 VOL  | T OR 3.3 VOLT AT BUS AND APLL II                                                              | NTERFACE       |                              |

| 3      | AT Bus Interface         | * A0, IOR, IOW, DACK, BALE                                                                    | 1              | VDDA5                        |

|        |                          | FIRQ, TC, OSC<br>* DB(0-7), DMA                                                               | O<br>I/O       | VDDA5<br>VDDA5               |

|        | APLL Interface Separator | * PLL24, PLLOUT<br>PLLIN, PLLREF                                                              | 0              | VDDA5<br>VDDA5               |

# **TABLE 3-4. SIGNAL GROUPS**

7-22 9/1/92

<sup>\*</sup> Input protection and internal pull-ups applicable to these signals are connected to VDDA5 or VDDD5 power pin.

Input receivers for these signals are powered by VDD3 power pin.

# 7

### 4.0 CHIP SELECT LOGIC

The Chip Select Logic is handled cooperatively by all the chips in the chip set, with each chip contributing its part to the logic. The WD76C10 and WD76C20ALV are particularly interrelated. Many of the decoding operations begun by the WD76C10 are handed to the WD76C20ALV for completion, and vice versa. For this reason, it is necessary to read both this section and section 7 of the WD76C10 for the fullest possible understanding of this function.

The Chip Select Logic of the WD76C20ALV provides decoding of five CSL input lines, DPH, DPL, RA10-8, into 17 output lines.

Figure 4-1 provides a block diagram of the inputs and outputs associated with this component.

Before the decoder can function, it must be enabled by  $\overline{\text{CSEN}}$  going active low and remains open until it is disabled by DACKEN going active high. Optionally, the chip select inputs ( $\overline{\text{CSEN}}$ , DPH, DPL, RA10, RA9, RA8) can be latched by dropping the BALE from 1 to 0. These latches are transparent when BALE is held high or left unconnected.

Once enabled, the Chip Select Logic provides decoding for the following signals, as shown in Table 4-1.

Table 4-2 lists the I/O addresses and chip selects generated for each fixed port. Address bits A15 through A10 are ignored for the I/O addresses listed with three digits. The ports are listed in the sequence of the chip select value.

FIGURE 4-1. CHIP SELECT BLOCK DIAGRAM

| CS# | DPH | CSL<br>DPL | INPUT LI | NES<br>RA9 | RA8 | FUNCTION                                                                                               |

|-----|-----|------------|----------|------------|-----|--------------------------------------------------------------------------------------------------------|

| 00H | 0   | 0          | 0        | 0          | 0   | Assert ROMOE to Output Enable the ROM BIOS <sup>1</sup>                                                |

| 01H | 0   | 0          | 0        | 0          | 1   | Assert CS8042 to Chip Select the Keyboard Control                                                      |

| 02H | 0   | 0          | 0        | 1          | 0   | Assert NPCS to Chip Select the Numeric Processor <sup>1</sup>                                          |

| 03H | 0   | 0          | 0        | 1          | 1   | Assert PCUW0 to Write Strobe PCU #0                                                                    |

| 04H | 0   | 0          | 1        | 0          | 0   | Assert LCLACK to acknowledge Keyboard Processor <sup>1</sup>                                           |

| 05H | 0   | 0          | 1        | 0          | 1   | Assert RTC ALE for RTC I/O <sup>1</sup>                                                                |

| 06H | 0   | 0          | 1        | 1          | 0   | Assert RTC Write Strobe Gated by CSEN & IOW <sup>1</sup>                                               |

| 07H | 0   | 0          | 1        | 1          | 1   | Assert RTC Read Stobe Gated by CSEN & IOR1                                                             |

| 08H | 0   | 1          | 0        | 0          | 0   | Assert FDC LDOR Register Select Line <sup>1</sup>                                                      |

| 09H | 0   | 1          | 0        | 0          | 1   | Assert FDC FDCS Chip Select Line <sup>1</sup>                                                          |

| 0AH | 0   | 1          | 0        | . 1        | 0   | Assert FDC LDCR Register (Read/Write) Select Line <sup>1</sup>                                         |

| овн | 0   | 1          | 0        | 1          | 1   | Assert FDC LDCR Register (Read/Write) Select Line & assert IDEDENL and CSIDE1 IDE Card Select Lines    |

| 0CH | 0   | 1          | 1        | 0          | 0   | Assert IDEDENL and CSIDEO IDE Card Select Line & assert IDEDENH if A0 = 01                             |

| ODH | 0   | 1          | 1        | 0          | 1   | Assert IDEDENL and CSIDE1 IDE Card Select Line1                                                        |

| 0EH | 0   | 1          | 1        | 1          | 0   | Assert CSSERA to Chip Select Serial Port A1                                                            |

| 0FH | 0   | 1          | 1        | 1          | 1   | Assert CSPAR0 to Chip Select Parallel Port 01                                                          |

| 10H | 1   | 0          | 0        | О          | 0   | Assert CSSERB to Chip Select Serial Port B1                                                            |

| 11H | 1   | 0          | 0        | 0          | 1   | Assert PROGCS <sup>1</sup>                                                                             |

| 14H | 1   | 0          | 1        | o          | 0   | Assert EMS to signify external EMS memory access <sup>1</sup>                                          |

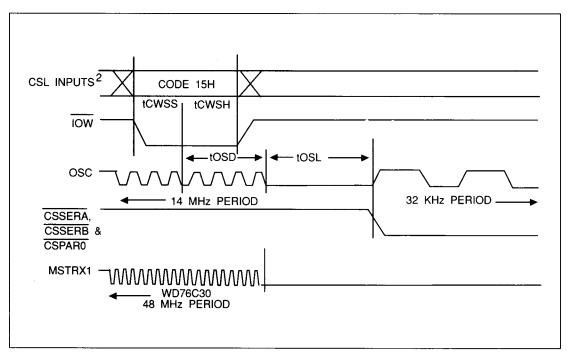

| 15H | 1   | 0          | 1        | 0          | 1   | WD76C30ALV 48 MHz Clk Disable , CSL Latches Cod<br>OSSERA, CSSERB & CSPAR0 stay asserted <sup>2</sup>  |

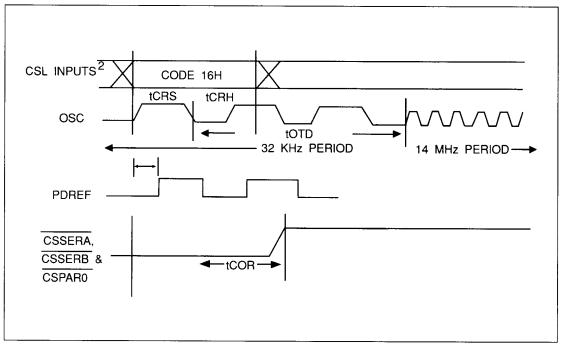

| 16H | 1   | 0          | 1        | 1          | 0   | 48 MHz Clk Enable for WD76C30ALV, CSL unlatches code, so CSSERA, CSSERB & CSPAR0 deassert <sup>3</sup> |

| 17H | 1   | 0          | 1        | 1          | 1   | Assert PCUW1 to Write Strobe PCU #1                                                                    |

| 18H | 1   | 1          | 0        | 0          | 0   | Reserved                                                                                               |

| 19H | 1   | 1          | 0        | 0          | 1   | Reserved                                                                                               |

| 1AH | 1   | 1          | О        | 1          | 0   | Assert PROG2 programmable chip select 2                                                                |

| 1BH | 1   | 1          | 0        | 1          | 1   | Assert PROG3 programmable chip select 3                                                                |

# TABLE 4-1. CHIP SELECT LINE DECODER

**%** 9/1/92 7-24

These signals are generated using latched CSL inputs if BALE is used.

Suspend Mode is entered by asserting code 15H on the CSL inputs, while qualifying it by CSEN=0, IOW=0, and the falling edge of OSC.

Suspend Mode is left by asserting code 16H on the CSL inputs, while qualifying it by an OSC falling edge.

| PORT                     | I/O ADDRESS           | CS#             | FUNCTION                                      |

|--------------------------|-----------------------|-----------------|-----------------------------------------------|

| ROM Chip Select          | N/A                   | 00              | Chip Select for BIOS ROM                      |

| Keyboard Control         | 060 - 06E<br>Even     | 01              | Chip Select For 8042                          |

| 80287                    | 00E0 - 00FF           | 02              | Chip Select for Numeric Processor             |

| Power Control            | 7072                  | 03              | PMC Write Strobe 0                            |

| Reserved                 |                       | 04              | Reserved                                      |

| Real Time Clock          | 070                   | 05              | RTC ALE                                       |

| Real Time Clock          | 071                   | 06              | RTC Write Stroke                              |

| Real Time Clock          | 071                   | 07              | RTC Read Strobe                               |

| Floppy Operation         | 3F2                   | 08              | Primary Address                               |

| Chip Select              | 372                   |                 | Secondary Address                             |

| Floppy Chip Select       | 3F4, 3F5              | 09              | Primary Address                               |

| '''                      | 374, 375              |                 | Secondary Address                             |

| Floppy Control           | 3F7                   | 0 <b>A</b>      | Primary Address                               |

| Chip Select              | 377                   |                 | Secondary Address                             |

|                          |                       |                 | (Floppy Enabled, HD Disabled)                 |

| Floppy And HD            |                       | 0B              | Primary Address                               |

| Control Chip Select      | 377                   |                 | Secondary Address                             |

| ll Di L OLI              |                       |                 | (Floppy Enabled, HD Enabled)                  |

| Hard Disk Chip           |                       | OC              | Primary Address                               |

| Select                   | 170, 171 - 177        | 0.5             | Secondary Address                             |

| Hard Disk Chip<br>Select | 376, 377 <sup>1</sup> | OD              | Primary Address, IDE Mode Only                |

| Serial Port A Chip       |                       | 0E <sup>2</sup> | Secondary Address, IDE Mode Only              |

| Select                   | 2F8 - 2FF             | UE              |                                               |

|                          | 3E8 - 3EF             |                 |                                               |

|                          | 3F8 - 3FF             |                 |                                               |

| Parallel Port 0          | 278 - 27F             | 0F              |                                               |

| Chip Select              | 378 - 37F             |                 |                                               |

|                          | 3BC - 3BF             |                 |                                               |

| Serial Port B Chip       |                       | 10 <sup>2</sup> |                                               |

| Select                   | 2F8 - 2FF             |                 |                                               |

|                          | 3E8 - 3EF             |                 |                                               |

| Program Chip             | 3F8 - 3FF             | 44              |                                               |

| Select Chip              | PROG                  | 11              |                                               |

| SCSI                     | 3530 - 353X           | 12              |                                               |

| Cache Flush              | F872                  | 13              |                                               |

| EMS                      | F012                  | 13              | Fire word FMO                                 |

| LIVIO                    | F072                  | 15              | External EMS                                  |

|                          | F472                  | 16              | 48 MHz Clock Disabled<br>48 MHz Clock Enabled |

| Power Control            | 7872                  | 17              | PMC Write Strobe 1                            |

| Reserved                 | . 0. 2                | 17<br>1E, 1F    | Reserved                                      |

|                          | PROG2,PROG3           | 1A, 1B          | I ICOCI VEU                                   |

| Select 2,3               |                       | 17, 15          |                                               |

TABLE 4-2. I/O ADDRESS AND CHIP SELECT ASSIGNMENTS

<sup>&</sup>lt;sup>1</sup> IDE Hard Disk enabled, floppy disabled <sup>2</sup> CS# is the decoded value of CS4-CS0.

### 5.0 FLOPPY DISK CONTROLLER

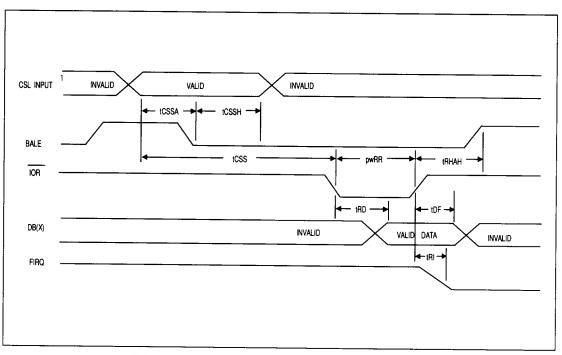

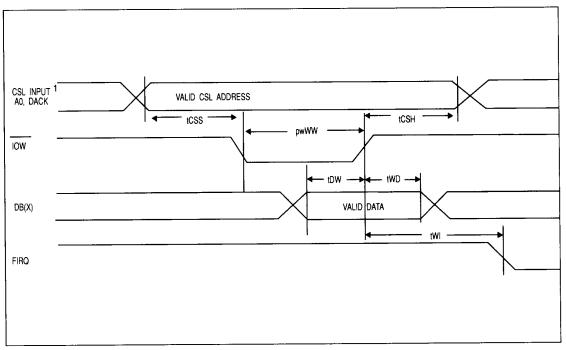

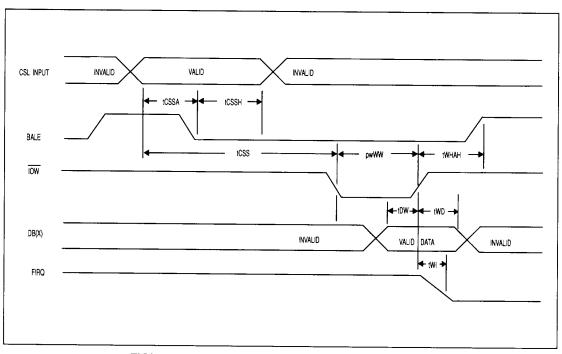

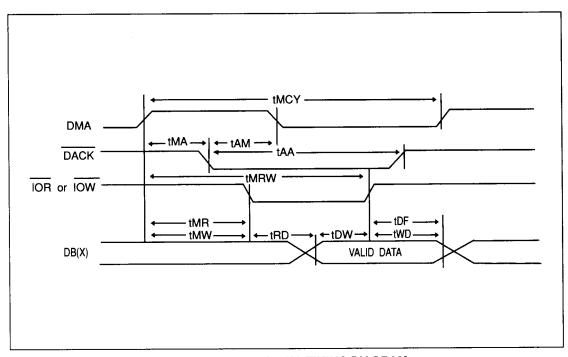

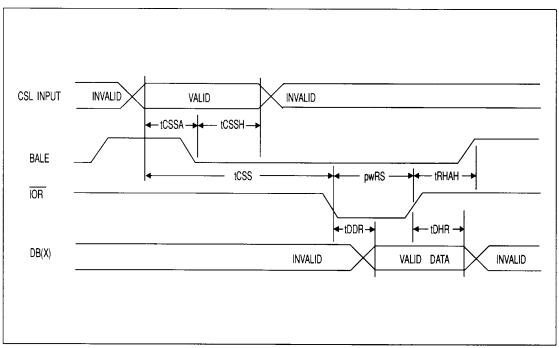

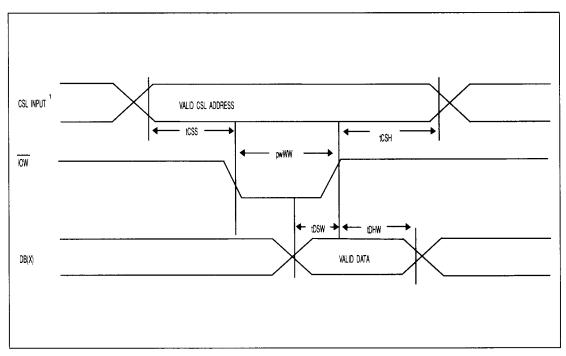

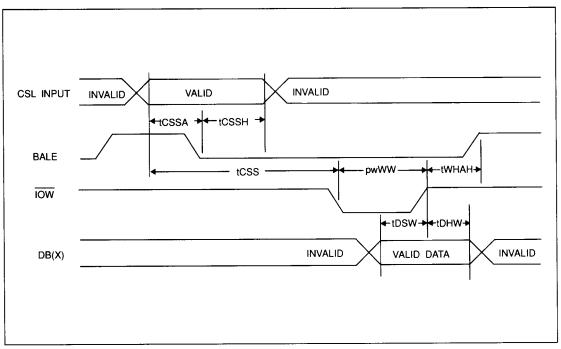

This section discusses the Floppy Disk Controller in detail. The Floppy Disk Controller (FDC) consists of several logical and/or physical blocks, as illustrated in Figure 5-2.

These components are:

- The 765A-compatible Core

- Clock & Timing Generator

- Drive Interface

- Data Separator

- Write Precompensator

- Host Interface