#### SiS5591/5592 SiS5595 OVERVIEW

SiS5591/5592 PCI A.G.P. & CPU Memory Controller

SiS5595 PCI SYSTEM I/O

The SiS5591/5592 SiS5595 glueless P5 A.G.P. chipset provides a high performance/cost index Desktop/Mobile solution for the Intel Pentium P54C/P55C, AMD K5/K6, and Cyrix M1/M2 A.G.P. system.

The SiS5591/SiS5592 A.G.P./PCI controller integrated the Host-to-PCI bridge, the L2 cache controller, the DRAM controller, the Accelerated Graphics Port interface, and the PCI IDE controller. The L2 cache controller can support up to 1 M P.B. SRAM, and the DRAM controller can support EDO/FP/SDRAM memory up to 768 MB with optional ECC or parity check function. The A.G.P. 1.0 compliance interface supports both 1X, and 2X speed mode with sideband address capability. The built-in fast PCI IDE controller supports the ATA PIO/DMA, and the Ultra DMA/33 functionality.

SiS5591 and SiS5592 have some pin-out switching to facilitate the main-board layout. SiS5591 pin assignment is based on the ATX form factor, and SiS5592 pin assignment is based on the NLX form factor. Beside the pin-out switching, SiS5591 and SiS5592 is totally the same on the internal logic circuit.

The SiS5595 PCI system I/O integrates the PCI-to-ISA bridge with the DDMA, and Serial IRQ capability, the ACPI/Legacy PMU, the Data Acquisition Interface, the Universal Serial Bus host/hub interface, and the ISA bus interface which contains the ISA bus controller, the DMA controllers, the interrupt controllers, and the Timers. It also integrates the Keyboard controller, and the Real Time Clock (RTC). The built-in USB controller, which is fully compliant to OHCI (Open Host Controller Interface), provides two USB ports capable of running full/low speed USB devices. The Data Acquisition Interface offers the ability of monitoring and reporting the environmental condition of the PC. It could monitor 4 positive analogue voltage inputs, 2 Fan speed inputs, and one temperature input.

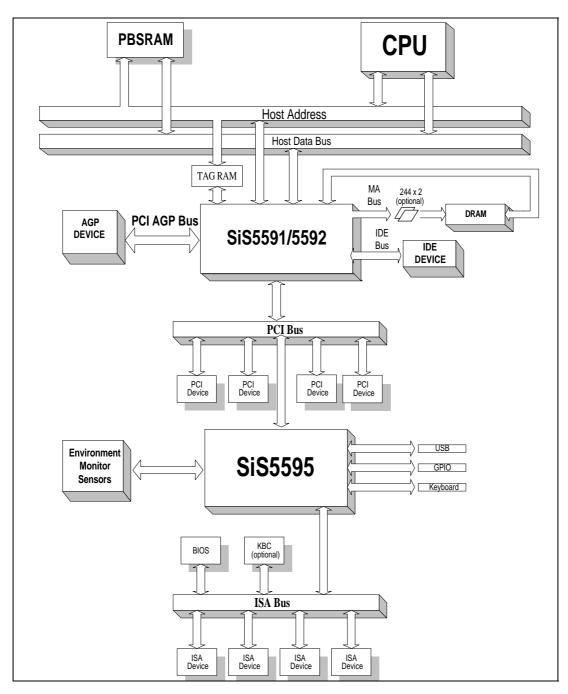

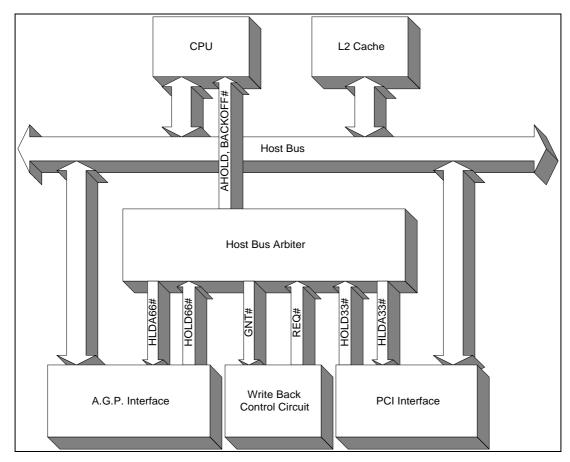

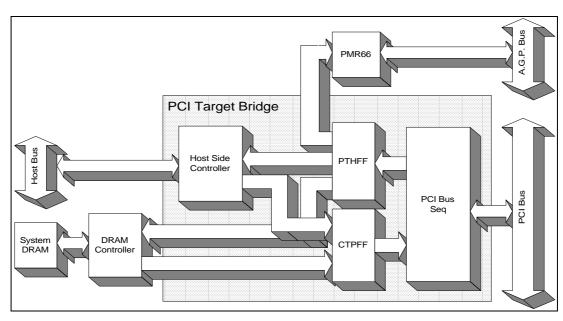

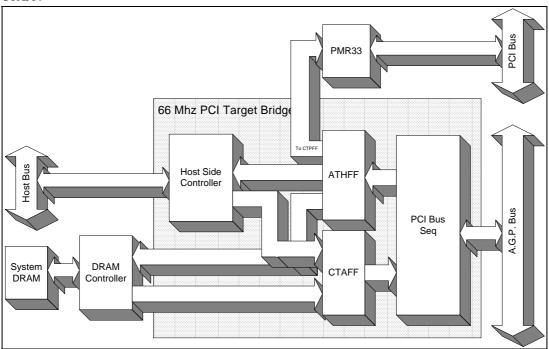

The following page will show the system block diagram.

Figure 1-1 SiS5591/5592 SiS5595 System Block Diagram

#### 2. FEATURE

#### 2.1 SiS5591/5592 PCI A.G.P. CONTROLLER

- Support Intel/AMD/Cyrix Pentium CPU and Other Compatible CPU Host Bus at 60/66 MHz and 3.3V Bus Interface

- Support the Pipelined Address of Pentium compatible CPU

- Support the Linear Address Mode of Cyrix CPU

- Support the Pipelined Address Mode of Pentium CPU

- **■** Fully Compliant to A.G.P. Revision 1.0 Specification

- **■** Meet PC97 Requirements

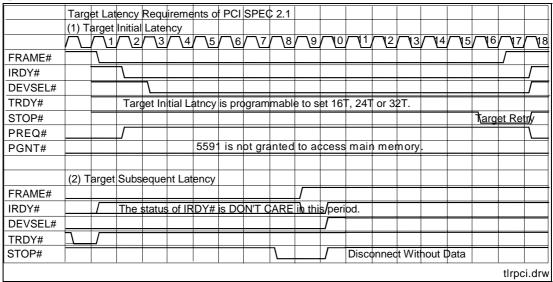

- Supports PCI Revision 2.1 Specification

- Integrated Second Level (L2) Cache Controller

- Write Back Cache Mode

- Support L2 Cache Flushing for entire L2 cache or specific 4K page

- 8 bits or 7 bits Tag with Direct Mapped Cache Organization

- Integrated 32K bits Dirty SRAM

- Integrated 32K bits Invalid SRAM

- Support Pipelined Burst SRAM

- Support 256K/512K/1MBytes Cache Sizes

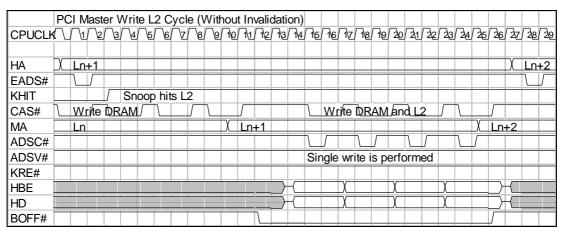

- Cache Hit Read/Write Cycle of 3-1-1-1

- Cache Back-to-Back Read/Write Cycle of 3-1-1-1-1-1

- Support Single Read Allocation for L2 Cache

- Support Concurrency of CPU to L2 cache and A.G.P. master to DRAM accesses

### **■ Integrated DRAM Controller**

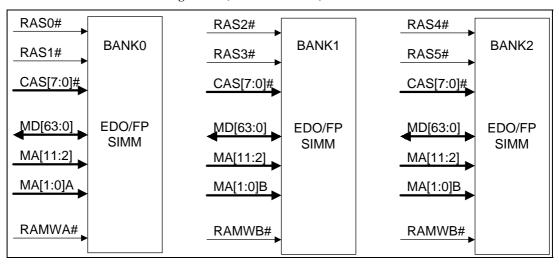

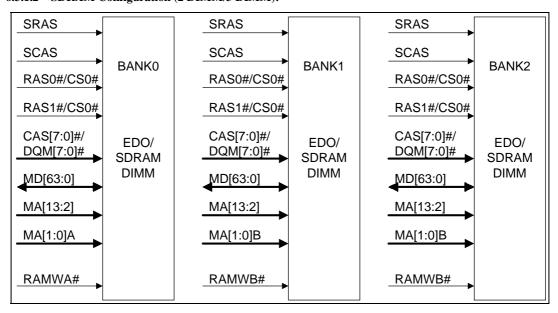

- Support 6 RAS Lines for FPM/EDO/SDRAM DIMMs/SIMMs

- Support 2Mbytes to 768Mbytes of main memory

- Support Cacheable DRAM Sizes up to 256 MBytes.

- Support 256K/512K/1M/2M/4M/8M/16Mx N FPM/EDO/SDRAM DRAM

- Support 64 Mb DRAM Technology

- Support Parity Checker or ECC Function

- Support 3.3V or 5V DRAM

- Supports Symmetrical and Asymmetrical DRAM

- Support Concurrent Write Back

- Support CAS before RAS Refresh, Self Refresh

- Support Relocation of System Management Memory

- Programmable CAS#, RAS#, RAMWE# and MA Driving Current

- Fully Configurable for the Characteristic of Shadow RAM ( 640 KBytes to 1 MBytes)

- Support FPM DRAM 5/6-3-3-3(-3-3-3) Burst Read Cycles

- Support EDO DRAM 5/6-2-2-2(-2-2-2) Burst Read Cycles

- Support SDRAM 5/6/7-1-1-1(-2/3-1-1-1) Burst Read Cycles

- Support X-1-1-1/X-2-2-2/X-3-3-3 Burst Write Cycles

- Two Programmable Non-cacheable Regions

- Option to Disable Local Memory in Non-cacheable Regions

- Shadow RAM in Increments of 16 Kbytes

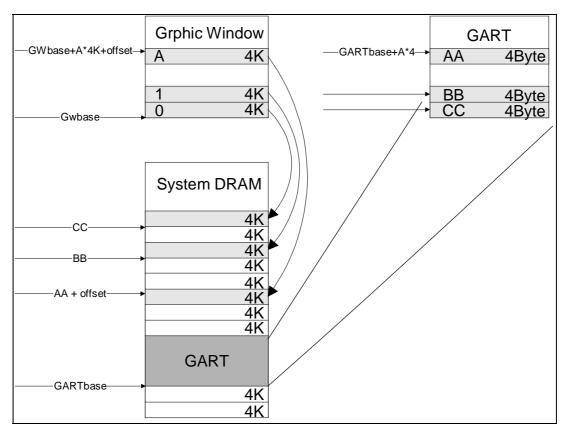

- Pseudo Directory/Page Scheme for Mapping Graphical Texture Access to Physical Memory Address

- Built-in 8 Way Associative/16 Entries GART cache to Minimize the Number of Memory Bus Cycles Required for Accessing Graphical Texture Memory

- Programmable Counters to Ensure Guaranteed Minimum Access Time for A.G.P., CPU, and PCI accesses

#### ■ Provides High Performance PCI Arbiter.

- Support up to 5 PCI Masters

- Support Rotating Priority Mechanism

- Hidden Arbitration Scheme Minimizes Arbitration Overhead.

- Support Concurrency between CPU to Memory and PCI to PCI

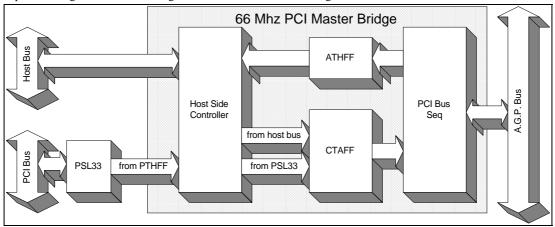

- Support Concurrency between CPU to 33Mhz PCI Access and 33Mhz PCI to A.G.P. Access

- Support Concurrency between CPU to 66Mhz PCI Access and A.G.P. to 33Mhz PCI Access

- Programmable Timers Ensure Guaranteed Minimum Access Time for PCI Bus Masters, and CPU

#### **■** Integrated Host-to-PCI Bridge

- Support Asynchronous and Synchronous PCI Clock

- Translates the CPU Cycles into the PCI Bus Cycles

- Zero Wait State Burst Cycles

- Support IDE Posted Write

- Support Pipelined Process in CPU-to-PCI Access

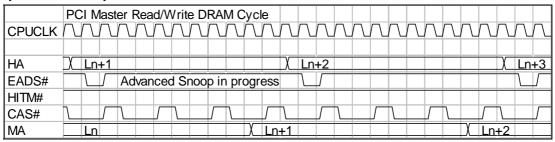

- Support Advance Snooping for PCI Master Bursting

- Maximum PCI Burst Transfer from 256 Bytes to 4 Kbytes

- Support Memory Remapping Function for PCI master accessing Graphical Window

#### ■ Integrated A.G.P. Compliant Target/66Mhz Host-to-PCI Bridge

- Support Asynchronous and Synchronous A.G.P. Clock

- Support 1X, and 2X Mode for A.G.P. 66/133 MHz 3.3V device

- Support Graphic Window Size from 4Mbytes to 256Mbytes

- Different arbitration policy for A.G.P. devices and 66Mhz PCI devices.

- Translates Sequential CPU-to-A.G.P. Memory Write Cycles into A.G.P. Bus (PCI66) Burst Cycles

- Zero Wait State Burst Cycles

- Support Pipelined Process in CPU-to-A.G.P. Access

- Support Advance Snooping for A.G.P. Master initiate system memory access with PCI Cycles

- Support 8 Way, 16 Entries Page Table Cache to enhance A.G.P. Read/Write Performance

- Support Both 1-Level and 2-Level GART(Graphic Address Re-Mapping Table)

- Maximum PCI Burst Transfer from 256 Bytes to 4 Kbytes

- Programmable Counters to Ensure Guaranteed Minimum Access Time for Low Priority Request, CPU to A.G.P./and A.G.P. Master Transaction

- Support PCI-to-PCI bridge function for memory write from 33Mhz PCI bus to A.G.P. bus

### ■ Integrated Posted Write Buffers and Read Prefetch Buffers to Increase System Performance

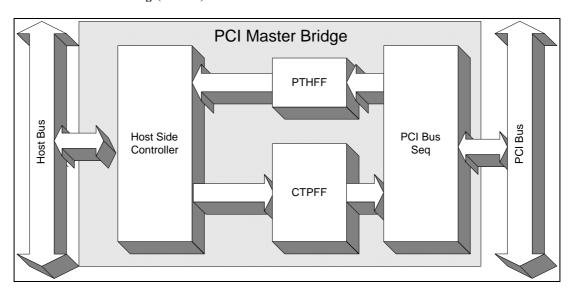

- CPU-to-Memory Posted Write Buffer (CTMFF) with 8 QW Deep, Always Sustains 0 Wait Performance on CPU-to-Memory

- CPU-to-Memory Read Buffer with 4 QW Deep

- CPU-to-PCI Posted Write Buffer(CTPFF) with 8 DW Deep

- PCI-to-Memory Posted Write Buffer(PTHFF) with 8 QW Deep, Always Streams 0 Wait Performance on PCI-to/from-Memory Access

- PCI-to-Memory Read Prefetch Buffer(CTPFF) with 8 QW Deep

- CPU-to-PCI66 Posted Write Buffer(CTAFF) with 8 DW Deep

- PCI66-to-Memory Posted Write Buffer(ATHFF) with 8 QW Deep

- A.G.P. Request Queue With the Depth of 32

- A.G.P. High Priority Write Queue with 64 QW Deep

- A.G.P. Low Priority Write Queue with 64 QW Deep

- A.G.P. High Priority Read Return Queue with 64 QW Deep

- A.G.P. Low Priority Read Return Queue with 64 QW Deep

#### **■ Fast PCI IDE Master/Slave Controller**

- Bus Master Programming Interface for ATA Windows 95 Compliant Controller

- Plug and Play Compatible

- Support Scatter and Gather

- Support Dual Mode Operation Native Mode and Compatibility Mode

- Support IDE PIO Timing Mode 0, 1, 2, 3 and 4

- Support Multiword DMA Mode 0, 1, 2

- Support Ultra DMA/33

- Two Separate IDE Bus

- Two 16 DW FIFO for PCI Burst Transfers.

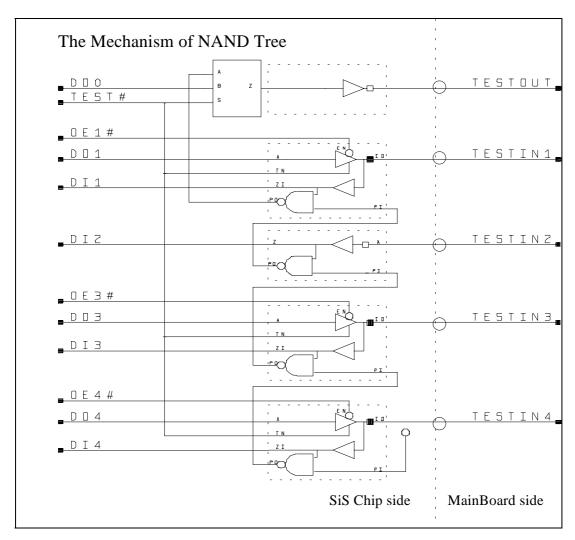

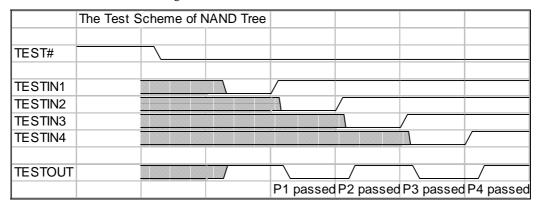

- Support NAND Tree for Ball Connectivity Testing

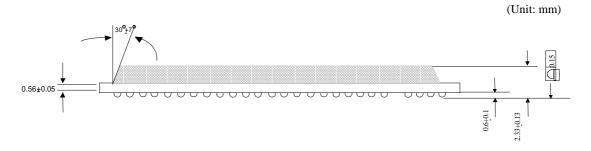

- 553-Balls BGA Package

- 0.35µm 3.3V CMOS Technology

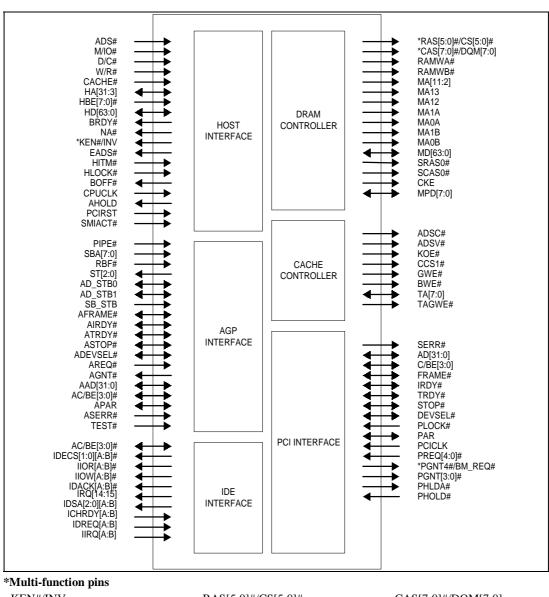

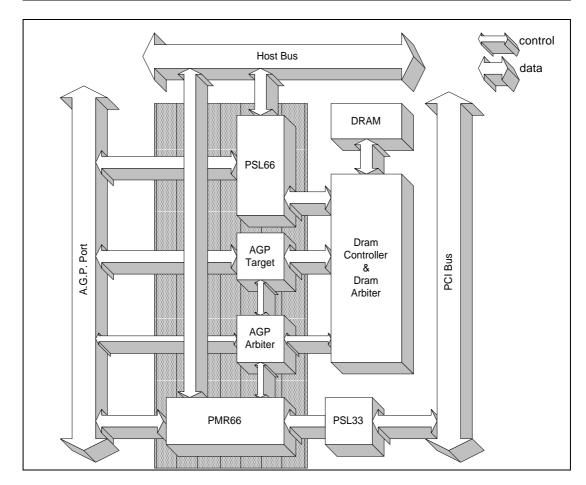

#### 2.2 FUNCTIONAL BLOCK DIAGRAM

\*Multi-function pins KEN#/INV PGNT4#/BM\_REQ#

RAS[5:0]#/CS[5:0]#

CAS[7:0]#/DQM[7:0]

Figure 2.2-1 SiS5591/5592 Functional Block Diagram

### 3. PIN ASSIGNMENT

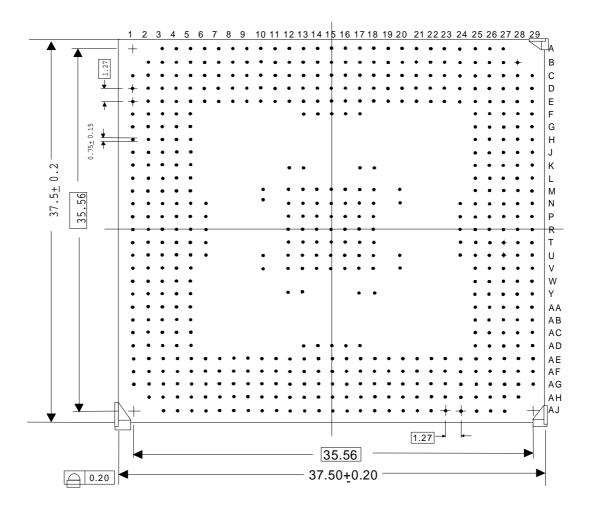

### 3.1 SiS5591 PIN ASSIGNMENT (TOP VIEW)

SiS5591 Pin Assignment (Top View-Left Side)

|    |          |         |          |           | CW Ec   |        |        |        |        |        |        |         |       |          |        |    |

|----|----------|---------|----------|-----------|---------|--------|--------|--------|--------|--------|--------|---------|-------|----------|--------|----|

|    | 1        | 2       | 3        | 4         | 5       | 6      | 7      | 8      | 9      | 10     | 11     | 12      | 13    | 14       | 15     |    |

| A  |          |         | NC       | M D l     | M D 35  | MD5    | M D 40 | MD9    | M D11  | M D13  | M D15  | M PD1   | CAS4# | RAS5#    | RAS1#  | A  |

| В  |          | M D 32  | MDO      | M D 34    | M D 3   | M D 38 | MD8    | MD10   | M D 44 | M D 46 | MPD4   | SCAS#   | CASO# | RAS4#    | RASO#  | В  |

| С  | NC       | 5VDD    | M D 33   | MD2       | M D 36  | MD6    | M D 41 | M D 43 | M D12  | M D14  | M PD 0 | RAMWA#  | CAS5# | RAS3#    | SRAS#  | С  |

| D  | SBA0     | ST2     | STl      | ST0       | MD4     | MD7    | VSSG   | VSSG   | VSSG   | M D 39 | M D 42 | M D 47  | CAS1# | RAS2#    | M A OB | D  |

| E  | SB_STB   | SBA3    | SBA2     | SBA1      | M D 37  | NC     | NC     | NC     | NC     | NC     | M D 45 | M PD5   | VSSG  | VSSG     | DVDD   | E  |

| F  | AGNT#    | SBA7    | SBA6     | SBA5      | SBA4    |        |        |        |        |        |        |         | NC    | NC       | DVDD   | F  |

| G  | AAD30    | AAD31   | P IP E#  | VSSG      | AREQ#   |        |        |        |        |        |        |         |       |          |        | G  |

| Н  | AAD27    | AAD28   | AAD29    | VSSG      | NC      |        |        |        |        |        |        |         |       |          |        | Н  |

| J  | AD_STB1  | AAD25   | AAD26    | RBF#      | NC      |        |        |        |        |        |        |         |       |          |        | J  |

| K  | AAD21    | AAD22   | AAD23    | AAD24     | NC      |        |        |        |        |        |        | OVDD3   | OVDD3 |          |        | К  |

| L  | AAD18    | AAD19   | AAD20    | AC/BE3#   | NC      |        |        |        |        |        |        |         |       |          |        | L  |

| М  | VREF     | VREFVSS | AC/BE2#  | AAD16     | AAD17   |        |        |        |        | OVDD3  |        | vss     | VSS   | OVDD2    | OVDD2  | М  |

| N  | ADEVSEL# | ATRDY#  | A IR DY# | VREFVDD   | AFRAME# | NC     |        |        |        | OVDD3  |        | VSS     | vss   | vss      | OVDD2  | N  |

| P  | AAD15    | AC/BE1# | ASTOP#   | APAR      | ASERR#  | NC     |        |        |        |        |        | VSS     | vss   | vss      | vss    | P  |

| R  |          | AAD12   | AAD13    | AAD14     | DVDD    | DVDD   |        |        |        |        |        | OVDD2   | OVDD2 | vss      | vss    | R  |

| т  | AC/BEO#  | AD_STB0 | AAD13    | AAD14     | AAD10   | NC     |        |        |        | -      |        | VSS     | vss   | vss      | vss    | т  |

|    |          |         |          | <b></b>   |         | NC NC  |        |        |        | OVDD3  |        | vss     |       | l        |        | ū  |

| U  | AAD3     | AAD4    | AAD5     | AAD6      | AAD7    | NC     |        |        |        |        |        |         | VSS   | vss      | OVDD2  |    |

| V  | BM_REQ#  | AAD0    | AAD1     | PHLDA#    | AAD2    |        |        |        |        | OVDD3  |        | VSS     | VSS   | OVDD2    | OVDD2  | V  |

| W  | AGPCLK   | PHOLD#  | PREQ4#   | TEST_P IN | PCRST#  |        |        |        |        | -      |        |         |       |          |        | W  |

| Y  | PLLVSS   | PLLVDD  | VSSP     | PGNT2#    | PGNT0#  |        |        |        |        |        |        | OVDD3   | OVDD3 |          |        | Y  |

| AA | PREQ 2#  | PREQ1#  | PREQ0#   | VSSG      | AD 29   |        |        |        |        |        |        |         |       |          |        | AA |

| AB | PGNT3#   | PREQ3#  | PGNT1#   | AD20      | C/BE3#  |        |        |        |        |        |        |         |       |          |        | AB |

| AC | AD28     | AD30    | AD31     | VSSG      | AD16    |        |        |        |        |        |        |         |       |          |        | AC |

| AD | AD23     | AD24    | AD 25    | AD26      | AD27    |        |        |        |        |        |        |         | DVDD  | DVDD     | DVDD   | AD |

| AE | AD18     | AD19    | AD21     | AD22      | AD12    | C/BE0# | PLOCK# | PAR    | AD9    | AD3    | DA8    | DA3     | IDRA  | DSA2A    | DVDD   | AE |

| AF | IRDY#    | FRAM E# | C/BE2#   | AD17      | AD11    | AD6    | STOP#  | AD13   | AD7    | IRQ14  | IDA10  | DA1     | DACKA | IDECS OA | IDB 6  | AF |

| AG | NC       | TR DY#  | 5VDD     | C/BE1#    | AD10    | AD5    | AD1    | DA7    | DA5    | IDA12  | DA14   | DREQA   | IRQA  | IDECS1A  | IDB9   | AG |

| AH |          | DEVSEL# | SERR#    | AD15      | AD8     | AD4    | AD0    | DA6    | DA4    | DA2    | DA0    | IDW A   | DSAlA | DB7      | IDB5   | AH |

| AJ |          |         | NC       | AD14      | PCICLK  | AD2    | IRQ15  | DA9    | IDA11  | IDA13  | IDA15  | ICHRDYA | DSA0A | DB8      | IDB10  | AJ |

|    | 1        | 2       | 3        | 4         | 5       | 6      | 7      | 8      | 9      | 10     | 11     | 12      | 13    | 14       | 15     |    |

Figure 3.1-0-1 SiS5591/5592 Pin Assignment (Left Side)

## SiS5591 Pin Assignment (Top View-Right Side)

|    |         |         |         | op viev  |           |        |       |         |        |         |        |          |          |         |    |

|----|---------|---------|---------|----------|-----------|--------|-------|---------|--------|---------|--------|----------|----------|---------|----|

|    | 16      | 17      | 18      | 19       | 20        | 21     | 22    | 23      | 24     | 25      | 26     | 27       | 28       | 29      |    |

| A  | M A O A | M A 3   | M A 7   | M All    | CAS6#     | RAMWB# | M PD2 | M D 48  | M D 20 | M D53   | M D 22 | NC       |          |         | A  |

| В  | MAlB    | M A 4   | M A 8   | M A 12   | CAS2#     | CKE    | MPD7  | MD16    | M D18  | M D21   | 5VD D  | M D 23   | M D 25   |         | В  |

| С  | MAlA    | M A 5   | M A 10  | M A 13   | CAS3#     | M PD 6 | M PD3 | M D 49  | M D51  | M D54   | M D 55 | M D 56   | M D 26   | NC      | С  |

| D  | MA2     | M A 6   | M A 9   | CAS7#    | VSSG      | VSSG   | VSSG  | M D17   | M D19  | M D57   | M D 29 | M D 28   | M D 60   | M D 27  | D  |

| E  | NC      | NC      | NC      | NC       | NC        | NC     | NC    | M D 5 0 | M D52  | M D 2 4 | HD0    | M D 31   | M D 3 0  | M D 62  | E  |

| F  | NC      | NC      |         |          |           |        |       |         |        | VSSG    | M D58  | HD5      | HD3      | HD1     | F  |

| G  |         |         |         |          |           |        |       |         |        | M D 5 9 | HD10   | HD9      | HD7      | HD6     | G  |

| Н  |         |         |         |          |           |        |       |         |        | M D 6 3 | M D 61 | HD13     | HD14     | HD12    | Н  |

| J  |         |         |         |          |           |        |       |         |        | HD4     | HD2    | HD17     | HD16     | HD18    | J  |

| K  |         | O VDD 3 | OVDD3   |          |           |        |       |         |        | HD11    | HD8    | HD19     | HD21     | HD20    | К  |

| L  |         |         |         |          |           |        |       |         |        | HD22    | HD15   | HD25     | HD26     | HD23    | L  |

| М  | VS S    | VSS     | VS S    |          | OVDD3     |        |       |         |        | HD28    | HD24   | HD29     | HD30     | HD27    | М  |

| N  | vs s    | VSS     | vss     |          | OVDD3     |        |       |         | DVDD   | HD31    | HD34   | HD35     | HD32     | HD33    | N  |

| р  | vs s    | vs s    | vss     |          |           |        |       |         | DVDD   | HD39    | HD42   | HD38     | HD36     | HD37    | P  |

| R  | vs s    | O VDD 2 | O VDD 2 |          |           |        |       |         | DVDD   | DVDD    | HD41   | HD44     | HD46     | HD40    | R  |

| т  | vs s    | vss     | vs s    |          |           |        |       |         | DVDD   | HD45    | HD50   | HD48     | HD47     | HD43    | т  |

| U  | VS S    | VSS     | vss     |          | OVDD3     |        |       |         | DVDD   | HD49    | HD53   | HD51     | HD52     | CPUCLK  | U  |

| v  | vs s    | VSS     | vss     |          | OVDD3     |        |       |         |        | HD60    | нд56   | HD57     | HD55     | HD54    | v  |

| W  |         |         |         |          |           |        |       |         |        | ADSC#   | HD63   | HD61     | HD59     | HD58    | W  |

| Y  |         | O VDD 3 | OVDD3   |          |           |        |       |         |        | TA 2    | TA 7   | BWE#     | GWE#     | HD62    | Y  |

| AA |         |         |         |          |           |        |       |         |        | BRDY#   | M /IO# | ccs1#    | ADV#     | KOE#    | AA |

| AB |         |         |         |          |           |        |       |         |        | EADS#   | HLOCK# | TA 5     | TA 6     | TAGW E# | AB |

| AC |         |         |         |          |           |        |       |         |        | HBE4#   | HBE1#  | TAl      | TA 3     | TA 4    | AC |

| AD | DVDD    | DVDD    |         |          |           |        |       |         |        | NA#     | AHOLD  | KEN#/INV | CACHE#   | TA 0    | AD |

| AE | IDB 4   | IDB14   | VSSG    | IDECS OB | HA25      | на6    | VSSG  | HA20    | на4    | НА9     | D /C#  | ADS#     | SM TACT# | BOFF#   | AE |

| AF | IDB11   | IDB13   | IRQB    | HA24     | HA30      | HA10   | HA16  | HBE6#   | на7    | HA12    | HBE2#  | нвео#    | W /R#    | H ITM # | AF |

| AG | IDB3    | DB1     | DREQB   | CHRDYB   | IDSA0B    | HA23   | HA22  | HA28    | HA5    | HA13    | на17   | HEB7#    | HBE3#    | NC      | AG |

| АН | IDB 12  | IDB0    | IIO W B | DACKB    | IDSA2B    | HA21   | HA26  | HA 29   | на 8   | HA15    | HA18   | HBE5#    | 5VDD     |         | AH |

| AJ | IDB2    | IDB15   | IDRB    | IDSA1B   | ID ECS 1B | HA27   | HA31  | наз     | HAll   | HA14    | HA19   | NC       |          |         | AJ |

|    | 16      | 17      | 18      | 19       | 20        | 21     | 22    | 23      | 24     | 25      | 26     | 27       | 28       | 29      |    |

Figure 3.1-0-2 SiS5591 Pin Assignment (Right Side)

### 3.2 SiS5592 PIN ASSIGNMENT (TOP VIEW)

SiS5592 Pin Assignment (Top View-Left Side)

|    |          |           | `        |           | CII DO  |        |        |        |        |        |        |         |        |          |        |    |

|----|----------|-----------|----------|-----------|---------|--------|--------|--------|--------|--------|--------|---------|--------|----------|--------|----|

|    | 1        | 2         | 3        | 4         | 5       | 6      | 7      | 8      | 9      | 10     | 11     | 12      | 13     | 14       | 15     |    |

| A  |          |           | NC       | AD14      | PCICLK  | AD2    | IRQ15  | DA9    | IDA11  | IDA13  | IDA15  | ICHRDYA | DSA0A  | DB8      | IDB10  | A  |

| В  |          | DEVSEL#   | SERR#    | AD15      | AD8     | AD4    | AD0    | DA6    | DA4    | IDA2   | DA0    | DOWA#   | DSA1A  | IDB7     | IDB5   | В  |

| С  | NC       | TRDY#     | 5VDD     | C/BE1#    | AD10    | AD5    | ADl    | DA7    | DA5    | IDA12  | DA14   | DREQA   | IRQA   | DECS1A#  | IDB9   | С  |

| D  | RDY#     | FRAME#    | C/BE2#   | AD17      | AD11    | AD6    | STOP#  | AD13   | AD7    | IRQ14  | IDA10  | DAl     | DACKA# | DECS OA# | IDB6   | D  |

| E  | AD18     | AD19      | AD21     | AD22      | AD12    | C/BE0# | PLOCK# | PAR    | AD9    | AD3    | DAS    | DA3     | IORA#  | IDSA2A   | DVDD   | E  |

| F  | AD23     | AD24      | AD25     | AD26      | AD27    |        |        |        |        |        |        |         | DVDD   | DVDD     | DVDD   | F  |

| G  | AD28     | AD30      | AD31     | VSSG      | AD16    |        |        |        |        |        |        |         |        |          |        | G  |

| Н  | PGNT3#   | PREQ3#    | PGNT1#   | AD20      | C/BE3#  |        |        |        |        |        |        |         |        |          |        | Н  |

| J  | PREQ 2#  | PREQ1#    | PREQ0#   | VSSG      | AD29    |        |        |        |        |        |        |         |        |          |        | J  |

| К  | PLLVSS   | PLLVDD    | VSSP     | PGNT2#    | PGNT0#  |        |        |        |        |        |        | OVDD3   | OVDD3  |          |        | К  |

| L  | AGPCLK   | PHOLD#    | PREQ4#   | TEST_P IN | PCRST#  |        |        |        |        |        |        |         |        |          |        | L  |

| М  | REQ#/PGN | AAD0      | AAD1     | PHLDA#    | AAD2    |        |        |        |        | OVDD3  |        | VSS     | VSS    | OVDD2    | OVDD2  | М  |

| N  | AAD3     | AAD4      | AAD5     | AAD6      | AAD7    | NC     |        |        |        | OVDD3  |        | VSS     | vss    | vss      | OVDD2  | N  |

| P  | AC/BEO#  | AD_STB0   | AAD8     | AAD9      | AAD10   | NC     |        |        |        |        |        | VSS     | vss    | vss      | vss    | P  |

| R  | AAD11    | AAD12     | AAD13    | AAD14     | DVDD    | DVDD   |        |        |        |        |        | OVDD2   | OVDD2  | vss      | vss    | R  |

| т  | AAD15    | AC/BE1#   | ASTOP#   | APAR      | ASERR#  | NC     |        |        |        |        |        | VSS     | VSS    | vss      | VSS    | т  |

| U  | ADEVSEL# | ATRDY#    | A IR DY# | VR EFVD D | AFRAME# | NC     |        |        |        | OVDD3  |        | vss     | vss    | vss      | OVDD2  | Ū  |

| v  | VREF     | VR EFVS S | AC/BE2#  | AAD16     | AAD17   |        |        |        |        | OVDD3  |        | VSS     | vss    | OVDD2    | OVDD2  | v  |

| W  | AAD18    | AAD19     | AAD20    | AC/BE3#   | NC      |        |        |        |        |        |        |         |        |          |        | W  |

| Y  | AAD21    | AAD22     | AAD23    | AAD24     | NC      |        |        |        |        |        |        | OVDD3   | OVDD3  |          |        | Y  |

| AA | AD_STB1  | AAD25     | AAD26    | RBF#      | NC      |        |        |        |        |        |        |         |        |          |        | AA |

| AB | AAD27    | AAD28     | AAD29    | VSSG      | NC      |        |        |        |        |        |        |         |        |          |        | AB |

| AC | AAD30    | AAD31     | P IP E#  | VSSG      | AREQ#   |        |        |        |        |        |        |         |        |          |        | AC |

| AD | AGNT#    | SBA7      | SBA6     | SBA5      | SBA4    |        |        |        |        |        |        |         | NC     | NC       | DVDD   | AD |

| AE | SB_STB   | SBA3      | SBA2     | SBA1      | M D 37  | NC     | NC     | NC     | NC     | NC     | M D 45 | M PD5   | VSSG   | VSSG     | DVDD   | AE |

| AF | SBA0     | ST2       | STl      | STO       | MD4     | MD7    | VSSG   | VSSG   | VSSG   | M D 39 | M D 42 | M D 47  | CAS1#  | RAS2#    | M A OB | AF |

| AG | NC       | 5VDD      | M D 33   | MD2       | M D 36  | MD6    | M D 41 | M D 43 | M D12  | M D14  | M PDO  | RAMWA#  | CAS5#  | RAS3#    | SRAS#  | AG |

| AH |          | M D 32    | MDO      | M D 34    | MD3     | M D 38 | MD8    | M D10  | M D 44 | M D 46 | MPD4   | SCAS#   | CAS0#  | RAS4#    | RASO#  | AН |

| AJ |          |           | NC       | MDl       | M D 35  | MD5    | M D 40 | MD9    | MD11   | M D 13 | M D 15 | M PD1   | CAS4#  | RAS5#    | RAS1#  | AJ |

|    | 1        | 2         | 3        | 4         | 5       | 6      | 7      | 8      | 9      | 10     | 11     | 12      | 13     | 14       | 15     |    |

Figure 3.2-0-1 SiS5592 Pin Assignment (Left Side)

### SiS5592 Pin Assignment (Top View-Right Side)

| 313339 | 16      | 17      | 18      | 19       | 20       | 21     | 22    | 23     | 24      | 25      | 26     | 27       | 28       | 29      |    |

|--------|---------|---------|---------|----------|----------|--------|-------|--------|---------|---------|--------|----------|----------|---------|----|

| A      | IDB 2   | IDB15   | DORB#   | DSAlB    | IDECS1B# | HA27   | HA31  | наз    | HAll    | HA14    | НА19   | NC       |          |         | A  |

| В      | IDB12   | IDB 0   | DOWB#   | DACKB#   | IDSA2B   | HA21   | HA26  | HA29   | HA8     | HA15    | HA18   | HBE5#    | 5VDD     |         | В  |

| С      | IDB 3   | IDB1    | DREQB   | CHRDYB   | IDSA0B   | HA23   | HA22  | HA28   | на5     | HA13    | HA17   | HEB7#    | HBE3#    | NC      | С  |

| D      | IDB11   | IDB13   | IRQB    | HA24     | HA30     | HA10   | HA16  | нве6#  | на7     | HA12    | HBE2#  | HBEO#    | W/R#     | H ITM # | D  |

| E      | IDB4    | IDB14   | VSSG    | IDECSOB# | H A 25   | на6    | VSSG  | HA20   | на4     | на9     | D /C#  | ADS#     | SM TACT# | BOFF#   | E  |

| F      | DVDD    | DVDD    |         |          |          |        |       |        |         | NA#     | AHOLD  | KEN#/INV | CACHE#   | TA 0    | F  |

| G      |         |         |         |          |          |        |       |        |         | HBE4#   | HBE1#  | TA1      | TA 3     | TA 4    | G  |

| Н      |         |         |         |          |          |        |       |        |         | EADS#   | HLOCK# | TA 5     | TA 6     | TAGW E# | Н  |

| J      |         |         |         |          |          |        |       |        |         | BRDY#   | M /IO# | ccs1#    | ADV#     | KOE#    | J  |

| K      |         | O VDD 3 | O VDD 3 |          |          |        |       |        |         | TA 2    | TA 7   | BWE#     | GW E#    | HD62    | К  |

| L      |         |         |         |          |          |        |       |        |         | ADSC#   | HD63   | HD61     | HD59     | HD58    | L  |

| М      | VS S    | vs s    | vss     |          | OVDD3    |        |       |        |         | HD60    | HD56   | HD57     | HD55     | HD54    | м  |

| N      | VS S    | VS S    | vss     |          | OVDD3    |        |       |        | DVDD    | HD49    | HD53   | HD51     | HD52     | CPUCLK  | N  |

| P      | VS S    | VS S    | vss     |          |          |        |       |        | DVDD    | HD45    | HD50   | HD48     | HD47     | HD43    | P  |

| R      | VSS     | O VDD 2 | OVDD2   |          |          |        |       |        | DVDD    | DVDD    | HD41   | HD44     | HD46     | HD40    | R  |

| Т      | vs s    | VSS     | VS S    |          |          |        |       |        | DVDD    | HD39    | HD42   | HD38     | HD36     | HD37    | т  |

| Ū      | VS S    | VSS     | VS S    |          | OVDD3    |        |       |        | DVDD    | HD31    | HD34   | HD35     | HD32     | HD33    | U  |

| v      | VSS     | VSS     | VSS     |          | OVDD3    |        |       |        |         | HD28    | HD24   | HD29     | HD30     | HD27    | v  |

| W      |         |         |         |          |          |        |       |        |         | HD22    | HD15   | HD25     | HD26     | HD23    | W  |

| Y      |         | O VDD 3 | O VDD 3 |          |          |        |       |        |         | HD11    | HD8    | HD19     | HD21     | HD20    | Y  |

| AA     |         |         |         |          |          |        |       |        |         | HD4     | HD2    | HD17     | HD16     | HD18    | AA |

| AB     |         |         |         |          |          |        |       |        |         | M D 6 3 | M D 61 | HD13     | HD14     | HD12    | AB |

| AC     |         |         |         |          |          |        |       |        |         | M D 5 9 | HD10   | HD9      | HD7      | HD6     | AC |

| AD     | NC      | NC      |         |          |          |        |       |        |         | VSSG    | M D 58 | HD5      | HD3      | HD1     | AD |

| ΑE     | NC      | NC      | NC      | NC       | NC       | NC     | NC    | M D 50 | M D 5 2 | M D 24  | HD0    | M D 31   | M D 30   | M D 62  | AE |

| AF     | M A 2   | M A 6   | M A 9   | CAS7#    | VSSG     | VSSG   | VSSG  | M D17  | M D19   | M D57   | M D 29 | M D 28   | M D 60   | M D 27  | AF |

| AG     | MAlA    | M A 5   | M A10   | M A13    | CAS3#    | M PD 6 | M PD3 | M D 49 | M D51   | M D54   | M D 55 | M D 56   | M D 26   | NC      | AG |

| АН     | MAlB    | M A 4   | M A 8   | M A 12   | CAS2#    | CKE    | M PD7 | MD16   | M D18   | M D 21  | 5VD D  | M D 23   | M D 25   |         | AH |

| AJ     | M A O A | M A 3   | M A 7   | M All    | CAS6#    | RAMWB# | M PD2 | M D 48 | M D 20  | M D53   | M D 22 | NC       |          |         | AJ |

|        | 16      | 17      | 18      | 19       | 20       | 21     | 22    | 23     | 24      | 25      | 26     | 27       | 28       | 29      |    |

Figure 3.2-2 SiS5592 Pin Assignment (Right Side)

### 3.3 SiS5591/5592 ALPHABETICAL PIN LIST

| SIGNAL         | SiS5591  | SiS5592  |

|----------------|----------|----------|

| NAME           | BALL NO. | BALL NO. |

| 5VDD           | B26      | AH26     |

| 5VDD           | C2       | AG2      |

| 5VDD           | AG3      | C3       |

| 5VDD           | AH28     | B28      |

| AAD0           | V2       | M2       |

| AAD1           | V3       | M3       |

| AAD2           | V5       | M5       |

| AAD3           | U1       | N1       |

| AAD4           | U2       | N2       |

| AAD5           | U3       | N3       |

| AAD6           | U4       | N4       |

| AAD7           | U5       | N5       |

| AAD8           | T3       | P3       |

| AAD9           | T4       | P4       |

| AAD10          | T5       | P4<br>P5 |

| AAD10<br>AAD11 | R1       | R1       |

| AAD11<br>AAD12 | R2       | R2       |

| AAD12<br>AAD13 | R3       | R3       |

| AAD13<br>AAD14 | R4       |          |

|                |          | R4<br>T1 |

| AAD16          | P1       | V4       |

| AAD16          | M4       |          |

| AAD17          | M5       | V5       |

| AAD18          | L1       | W1       |

| AAD19          | L2       | W2       |

| AAD20          | L3       | W3       |

| AAD21          | K1       | Y1       |

| AAD22          | K2       | Y2       |

| AAD23          | K3       | Y3       |

| AAD24          | K4       | Y4       |

| AAD25          | J2       | AA2      |

| AAD26          | J3       | AA3      |

| AAD27          | H1       | AB1      |

| AAD28          | H2       | AB2      |

| AAD29          | H3       | AB3      |

| AAD30          | G1       | AC1      |

| AAD31          | G2       | AC2      |

| AC/BE0#        | T1       | P1       |

| AC/BE1#        | P2       | T2       |

| AC/BE2#        | M3       | V3       |

| AC/BE3#        | L4       | W4       |

| AD_STB0        | T2       | P2       |

| AD_STB1        | J1       | AA1      |

| AD00           | AH7      | B7       |

| AD01           | AG7      | C7       |

| AD02           | AJ6      | A6       |

| AD03           | AE10     | E10      |

| AD04           | AH6      | B6       |

| AD05           | AG6      | C6       |

| AD06           | AF6      | D6       |

| GEGNIA    | C'CEE01  | G'GFF02  |

|-----------|----------|----------|

| SIGNAL    | SiS5591  | SiS5592  |

| NAME      | BALL NO. | BALL NO. |

| AD07      | AF9      | D9       |

| AD08      | AH5      | B5       |

| AD09      | AE9      | E9       |

| AD10      | AG5      | C5       |

| AD11      | AF5      | D5       |

| AD12      | AE5      | E5       |

| AD13      | AF8      | D8       |

| AD14      | AJ4      | A4       |

| AD15      | AH4      | B4       |

| AD16      | AC5      | G5       |

| AD17      | AF4      | D4       |

| AD18      | AE1      | E1       |

| AD19      | AE2      | E2       |

| AD20      | AB4      | H4       |

| AD21      | AE3      | E3       |

| AD22      | AE4      | E4       |

| AD23      | AD1      | F1       |

| AD24      | AD2      | F2       |

| AD25      | AD3      | F3       |

| AD26      | AD4      | F4       |

| AD27      | AD5      | F5       |

| AD28      | AC1      | G1       |

| AD29      | AA5      | J5       |

| AD30      | AC2      | G2       |

| AD31      | AC3      | G3       |

| ADEVSEL#  | N1       | U1       |

| ADS#      | AE27     | E27      |

| ADSC#     | W25      | L25      |

| ADV#      | AA28     | J28      |

| AFRAME#   | N5       | U5       |

| AGNT#     | F1       | AD1      |

| A.G.P.CLK | W1       | L1       |

| AHOLD     | AD26     | F26      |

| AIRDY#    | N3       | U3       |

| APAR      | P4       | T4       |

| AREQ#     | G5       | AC5      |

| ASERR#    | P5       | T5       |

| ASTOP#    | P3       | T3       |

| ATRDY#    | N2       | U2       |

| BM_REQ#/  | V1       | M1       |

| BOFF#     | AE29     | E29      |

| BRDY#     | AA25     | J25      |

| BWE#      | Y27      | K27      |

| C/BE0#    | AE6      | E6       |

| C/BE1#    | AG4      | C4       |

| C/BE2#    | AF3      | D3       |

| C/BE3#    | AB5      | H5       |

| CACHE#    | AD28     | F28      |

| SIGNAL     | SiS5591  | SiS5592  |

|------------|----------|----------|

| NAME       | BALL NO. | BALL NO. |

| CAS0#DQM   | B13      | AH13     |

| CAS1#/DQM  | D13      | AF13     |

| CAS2#/DOM2 | B20      | AH20     |

| CAS3#/DOM3 | C20      | AG20     |

| CAS4#/DQM4 | A13      | AJ13     |

| CAS5#/DQM5 | C13      | AG13     |

| CAS6#/DOM6 | A20      | AJ20     |

| CAS7#/DOM7 | D19      | AF19     |

| CCS1#      | AA27     | J27      |

| CKE        | B21      | AH21     |

| CPUCLK     | U29      | N29      |

| D/C#       | AE26     | E26      |

| DEVSEL#    | AH2      | B2       |

| DVDD       | E15      | AE15     |

| DVDD       | F15      | AD15     |

| DVDD       | N24      | U24      |

| DVDD       | P24      | T24      |

| DVDD       | R5       | R5       |

| DVDD       | R6       | R6       |

| DVDD       | R24      | R24      |

| DVDD       | R25      | R25      |

| DVDD       | T24      | P24      |

| DVDD       | U24      | N24      |

| DVDD       | AD13     | F13      |

| DVDD       | AD13     | F14      |

| DVDD       | AD15     | F15      |

| DVDD       | AD16     | F16      |

| DVDD       | AD17     | F17      |

| DVDD       | AE15     | E15      |

| EADS#      | AB25     | H25      |

| FRAME#     | AF2      | D2       |

| GWE#       | Y28      | K28      |

| HA3        | AJ23     | A23      |

| HA4        | AE24     | E24      |

| HA5        | AG24     | C24      |

| HA6        | AE21     | E21      |

| HA7        | AF24     | D24      |

| HA8        | AH24     | B24      |

| HA9        | AE25     | E25      |

| HA10       | AF21     | D21      |

| HA11       | AJ24     | A24      |

| HA12       | AF25     | D25      |

| HA13       | AG25     | C25      |

| HA14       | AJ25     | A25      |

| HA15       | AH25     | B25      |

| HA16       | AF22     | D22      |

| HA17       | AG26     | C26      |

| HA18       | AH26     | B26      |

| HA19       | AJ26     | A26      |

| HA20       | AE23     | E23      |

| HA21       | AH21     | B21      |

| II.        | =        |          |

| SIGNAL | SiS5591  | SiS5592  |

|--------|----------|----------|

| NAME   | BALL NO. | BALL NO. |

| HA22   | AG22     | C22      |

| HA23   | AG21     | C21      |

| HA24   | AF19     | D19      |

| HA25   | AE20     | E20      |

| HA26   | AH22     | B22      |

| HA27   | AJ21     | A21      |

| HA28   | AG23     | C23      |

| HA29   | AH23     | B23      |

| HA30   | AF20     | D20      |

| HA31   | AJ22     | A22      |

| HBE0#  | AF27     | D27      |

| HBE1#  | AC26     | G26      |

| HBE2#  | AF26     | D26      |

| HBE3#  | AG28     | C28      |

| HBE4#  | AC25     | G25      |

| HBE5#  | AH27     | B27      |

| HBE6#  | AF23     | D23      |

| HBE7#  | AG27     | C27      |

| HD0    | E26      | AE26     |

| HD1    | F29      | AD29     |

| HD2    | J26      | AA26     |

| HD3    | F28      | AD28     |

| HD4    | J25      | AA25     |

| HD5    | F27      | AD27     |

| HD6    | G29      | AC29     |

| HD7    | G28      | AC28     |

| HD8    | K26      | Y26      |

| HD9    | G27      | AC27     |

| HD10   | G26      | AC26     |

| HD11   | K25      | Y25      |

| HD12   | H29      | AB29     |

| HD13   | H27      | AB27     |

| HD14   | H28      | AB28     |

| HD15   | L26      | W26      |

| HD16   | J28      | AA28     |

| HD17   | J27      | AA27     |

| HD18   | J29      | AA29     |

| HD19   | K27      | Y27      |

| HD20   | K29      | Y29      |

| HD21   | K28      | Y28      |

| HD22   | L25      | W25      |

| HD23   | L29      | W29      |

| HD24   | M26      | V26      |

| HD25   | L27      | W27      |

| HD26   | L28      | W28      |

| HD27   | L29      | W29      |

| HD28   | M25      | V25      |

| HD29   | M27      | V27      |

| HD30   | M28      | V28      |

| SIGNAL  | SiS5591  | SiS5592  |

|---------|----------|----------|

| NAME    | BALL NO. | BALL NO. |

| HD31    | N25      | U25      |

| HD32    | N28      | U28      |

| HD33    | N29      | U29      |

| HD34    | N26      | U26      |

| HD35    | N27      | U27      |

| HD36    | P28      | T28      |

| HD37    | P29      | T29      |

| HD38    | P27      | T27      |

| HD39    | P25      | T25      |

| HD40    | R29      | R29      |

| HD41    | R26      | R26      |

| HD42    | P26      | T26      |

| HD43    | T29      | P29      |

| HD44    | R27      | R27      |

| HD45    | T25      | P25      |

| HD46    | R28      | R28      |

| HD47    | T28      | P28      |

| HD48    | T27      | P27      |

| HD49    | U25      | N25      |

| HD50    | T26      | P26      |

| HD51    | U27      | N27      |

| HD52    | U28      | N28      |

| HD53    | U26      | N26      |

| HD54    | V29      | M29      |

| HD55    | V28      | M28      |

| HD56    | V26      | M26      |

| HD57    | V27      | M27      |

| HD58    | W29      | L29      |

| HD59    | W28      | L28      |

| HD60    | V25      | M25      |

| HD61    | W27      | L27      |

| HD62    | Y29      | K29      |

| HD63    | W26      | L26      |

| HITM#   | AF29     | D29      |

| HLOCK#  | AB26     | H26      |

| ICHRDYA | AJ12     | A12      |

| ICHRDYB | AG19     | C19      |

| IDACKA# | AF13     | D13      |

| IDACKB# | AH19     | B19      |

| IDA0    | AH11     | B11      |

| IDA1    | AF12     | D12      |

| IDA2    | AH10     | B10      |

| IDA3    | AE12     | E12      |

| IDA4    | AH9      | B9       |

| IDA5    | AG9      | C9       |

| IDA6    | AH8      | B8       |

| IDA7    | AG8      | C8       |

| IDA8    | AE11     | E11      |

| IDA9    | AJ8      | A8       |

| SIGNAL   | SiS5591  | SiS5592  |

|----------|----------|----------|

| NAME     | BALL NO. | BALL NO. |

| IDA10    | AF11     | D11      |

| IDA11    | AJ9      | A9       |

| IDA12    | AG10     | C10      |

| IDA13    | AJ10     | A10      |

| IDA14    | AG11     | C11      |

| IDA15    | AJ11     | A11      |

| IDB0     | AH17     | B17      |

| IDB1     | AG17     | C17      |

| IDB2     | AJ16     | A16      |

| IDB3     | AG16     | C16      |

| IDB4     | AE16     | E16      |

| IDB5     | AH15     | B15      |

| IDB6     | AF15     | D15      |

| IDB7     | AH14     | B14      |

| IDB8     | AJ14     | A14      |

| IDB9     | AG15     | C15      |

| IDB10    | AJ15     | A15      |

| IDB11    | AF16     | D16      |

| IDB12    | AH16     | B16      |

| IDB13    | AF17     | D17      |

| IDB14    | AE17     | E17      |

| IDB15    | AJ17     | A17      |

| IDECS0A# | AF14     | D14      |

| IDECS1A# | AG14     | C14      |

| IDECS0B# | AE19     | E19      |

| IDECS1B# | AJ20     | A20      |

| IDREQA#  | AG12     | C12      |

| IDREQB#  | AG18     | C18      |

| IDSA0A   | AJ13     | A13      |

| IDSA1A   | AH13     | B13      |

| IDSA2A   | AE14     | E14      |

| IDSA0B   | AG20     | C20      |

| IDSA1B   | AJ19     | A19      |

| IDSA2B   | AH20     | B20      |

| IIORA    | AE13     | E13      |

| IIORB    | AJ18     | A18      |

| IIOWA    | AH12     | B12      |

| IIOWB    | AH18     | B18      |

| IIRQA    | AG13     | C13      |

| IIRQB    | AF18     | D18      |

| IRDY#    | AF1      | D1       |

| IRQ14    | AF10     | D10      |

| IRQ15    | AJ7      | A7       |

| KEN#/INV | AD27     | F27      |

| KOE#     | AA29     | J29      |

| M/IO#    | AA26     | J26      |

| MA0A     | A16      | AJ16     |

| MA0B     | D15      | AF15     |

| MA1A     | C16      | AG16     |

| SIGNAL | SiS5591  | SiS5592  |

|--------|----------|----------|

| NAME   | BALL NO. | BALL NO. |

| MA1B   | B16      | AH16     |

| MA2    | D16      | AF16     |

| MA3    | A17      | AJ17     |

| MA4    | B17      | AH17     |

| MA5    | C17      | AG17     |

| MA6    | D17      | AF17     |

| MA7    | A18      | AJ18     |

| MA8    | B18      | AH18     |

| MA9    | D18      | AF18     |

| MA10   | C18      | AG18     |

| MA11   | A19      | AJ19     |

| MA12   | B19      | AH19     |

| MA13   | C19      | AG19     |

| MD0    | B3       | AH3      |

| MD1    | A4       | AJ4      |

| MD2    | C4       | AG4      |

| MD3    | B5       | AH5      |

| MD4    | D5       | AF5      |

| MD5    | A6       | AJ6      |

| MD6    | C6       | AG6      |

| MD7    | D6       | AF6      |

| MD8    | B7       | AH7      |

| MD9    | A8       | AJ8      |

| MD10   | B8       | AH8      |

| MD11   | A9       | AJ9      |

| MD12   | C9       | AG9      |

| MD13   | A10      | AJ10     |

| MD14   | C10      | AG10     |

| MD15   | A11      | AJ11     |

| MD16   | B23      | AH23     |

| MD17   | D23      | AF23     |

| MD18   | B24      | AH24     |

| MD19   | D24      | AF24     |

| MD20   | A24      | AJ24     |

| MD21   | B25      | AH25     |

| MD22   | A26      | AJ26     |

| MD23   | B27      | AH27     |

| MD24   | E25      | AE25     |

| MD25   | B28      | AH28     |

| MD26   | C28      | AG28     |

| MD27   | D29      | AF29     |

| MD28   | D27      | AF27     |

| MD29   | D26      | AF26     |

| MD30   | E28      | AE28     |

| MD31   | E27      | AE27     |

| MD32   | B2       | AH2      |

| MD33   | C3       | AG3      |

| MD34   | B4       | AH4      |

| MD35   | A5       | AJ5      |

| SIGNAL       | SiS5591    | SiS5592      |

|--------------|------------|--------------|

| NAME         | BALL NO.   | BALL NO.     |

| MD36         | C5         | AG5          |

| MD37         | E5         | AE5          |

| MD38         | B6         | AH6          |

| MD39         | D10        | AF10         |

| MD40         | A7         | AJ7          |

| MD40<br>MD41 | C7         | AG7          |

| MD42         | D11        | AF11         |

| MD43         | C8         | AG8          |

| MD44         | B9         | AH9          |

| MD45         | E11        | AE11         |

| MD45         | B10        | AH10         |

| MD47         | D12        |              |

|              | A23        | AF12         |

| MD48         |            | AJ23         |

| MD49         | C23        | AG23         |

| MD50         | E23        | AE23         |

| MD51<br>MD52 | C24<br>E24 | AG24<br>AE24 |

|              | _          |              |

| MD53         | A25        | AJ25         |

| MD54         | C25        | AG25         |

| MD55         | C26        | AG26         |

| MD56         | C27        | AG27         |

| MD57         | D25        | AF25         |

| MD58         | F26        | AD26         |

| MD59         | G25        | AC25         |

| MD60         | D28        | AF28         |

| MD61         | H26        | AB26         |

| MD62         | E29        | AE29         |

| MD63         | H25        | AB25         |

| MPD0         | C11        | AG11         |

| MPD1         | A12        | AJ12         |

| MPD2         | A22        | AJ22         |

| MPD3         | C22        | AG22         |

| MPD4         | B11        | AH11         |

| MPD5         | E12        | AE12         |

| MPD6         | C21        | AG21         |

| MPD7         | B22        | AH22         |

| NA#          | AD25       | F25          |

| NC           | A3         | AJ3          |

| NC           | A27        | AJ27         |

| NC           | C1         | AG1          |

| NC           | C29        | AG29         |

| NC           | E6         | AE6          |

| NC           | E7         | AE7          |

| NC           | E8         | AE8          |

| NC           | E9         | AE9          |

| NC           | E10        | AE10         |

| NC           | E16        | AE16         |

| NC           | E17        | AE17         |

| NC           | E18        | AE18         |

| SIGNAL  | SiS5591  | SiS5592  |

|---------|----------|----------|

| NAME    | BALL NO. | BALL NO. |

| NC      | E19      | AE19     |

| NC      | E20      | AE20     |

| NC      | E21      | AE21     |

| NC      | E22      | AE22     |

| NC      | F13      | AD13     |

| NC      | F14      | AD14     |

| NC      | F16      | AD16     |

| NC      | F17      | AD17     |

| NC      | Н5       | AB5      |

| NC      | J5       | AA5      |

| NC      | K5       | Y5       |

| NC      | L5       | W5       |

| NC      | N6       | U6       |

| NC      | P6       | T6       |

| NC      | T6       | P6       |

| NC      | U6       | N6       |

| NC      | AG1      | C1       |

| NC      | AG29     | C29      |

| NC      | AJ3      | A3       |

| NC      | AJ27     | A27      |

| OVDD2   | M14      | V14      |

| OVDD2   | M15      | V15      |

| OVDD2   | N15      | U15      |

| OVDD2   | U15      | N15      |

| OVDD2   | R12      | R12      |

| OVDD2   | R13      | R13      |

| OVDD2   | R17      | R17      |

| OVDD2   | R18      | R18      |

| OVDD2   | V14      | M14      |

| OVDD2   | V15      | M15      |

| OVDD3   | K12      | Y12      |

| OVDD3   | K13      | Y13      |

| OVDD3   | K17      | Y17      |

| OVDD3   | K18      | Y18      |

| OVDD3   | M10      | V10      |

| OVDD3   | M20      | V20      |

| OVDD3   | N10      | U10      |

| OVDD3   | N20      | U20      |

| OVDD3   | U10      | N10      |

| OVDD3   | U20      | N20      |

| OVDD3   | V10      | M10      |

| OVDD3   | V20      | M20      |

| OVDD3   | Y12      | K12      |

| OVDD3   | Y13      | K13      |

| OVDD3   | Y17      | K17      |

| OVDD3   | Y18      | K18      |

| PAR     | AE8      | E8       |

| PCICLK  | AJ5      | A5       |

| PCIRST# | W5       | L5       |

| SIGNAL     | SiS5591  | SiS5592  |

|------------|----------|----------|

| NAME       | BALL NO. | BALL NO. |

| PGNT0#     | Y5       | K5       |

| PGNT1#     | AB3      | H3       |

| PGNT2#     | Y4       | K4       |

| PGNT3#     | AB1      | H1       |

| PHLDA#     | V4       | M4       |

| PHOLD#     | W2       | L2       |

| PIPE#      | G3       | AC3      |

| PLLVDD     | Y2       | K2       |

| PLLVSS     | Y1       | K1       |

| PLOCK#     | AE7      | E7       |

| PREQ0#     | AA3      | J3       |

| PREQ1#     | AA2      | J2       |

| PREQ2#     | AA1      | J1       |

| PREQ3#     | AB2      | H2       |

| PREQ4#     | W3       | L3       |

| RAMWA#     | C12      | AG12     |

| RAMWB#     | A21      | AJ21     |

| RAS0#/CS0# | B15      | AH15     |

| RAS1#/CS1# | A15      | AJ15     |

| RAS2#/CS2# | D14      | AF14     |

| RAS3#/CS3# | C14      | AG14     |

| RAS4#/CS4# | B14      | AH14     |

| RAS5#/CS5# | A14      | AJ14     |

| RBF#       | J4       | AA4      |

| SBA0       | D1       | AF1      |

| SBA1       | E4       | AE4      |

| SBA2       | E3       | AE3      |

| SBA3       | E2       | AE2      |

| SBA4       | F5       | AD5      |

| SBA5       | F4       | AD4      |

| SBA6       | F3       | AD3      |

| SBA7       | F2       | AD2      |

| SB_STB     | E1       | AE1      |

| SCAS#      | B12      | AH12     |

| SERR#      | AH3      | B3       |

| SMIACT#    | AE28     | E28      |

| SRAS#      | C15      | AG15     |

| STOP#      | AF7      | D7       |

| ST0        | D4       | AF4      |

| ST1        | D3       | AF3      |

| ST2        | D2       | AF2      |

| TAGWE#     | AB29     | H29      |

| TA0        | AD29     | F29      |

| TA1        | AC27     | G27      |

| TA2        | Y25      | K25      |

| TA3        | AC28     | G28      |

| TA4        | AC29     | G29      |

| TA5        | AB27     | H27      |

| TA6        | AB28     | H28      |

| SIGNAL    | SiS5591  | SiS5592  |

|-----------|----------|----------|

| NAME      | BALL NO. | BALL NO. |

| TA7       | Y26      | K26      |

| TEST_PIN# | W4       | L4       |

| TRDY#     | AG2      | C2       |

| VREF      | M1       | V1       |

| VREFVDD   | N4       | U4       |

| VREFVSS   | M2       | V2       |

| VSS       | M12      | V12      |

| VSS       | M13      | V13      |

| VSS       | M16      | V16      |

| VSS       | M17      | V17      |

| VSS       | M18      | V18      |

| VSS       | N12      | U12      |

| VSS       | N13      | U13      |

| VSS       | N14      | U14      |

| VSS       | N16      | U16      |

| VSS       | N17      | U17      |

| VSS       | N18      | U18      |

| VSS       | P12      | T12      |

| VSS       | P13      | T13      |

| VSS       | P14      | T14      |

| VSS       | P15      | T15      |

| VSS       | P16      | T16      |

| VSS       | P17      | T17      |

| VSS       | P18      | T18      |

| VSS       | R14      | R14      |

| VSS       | R15      | R15      |

| VSS       | R16      | R16      |

| VSS       | T12      | P12      |

| VSS       | T13      | P13      |

| VSS       | T14      | P14      |

| VSS       | T15      | P15      |

| VSS       | T16      | P16      |

| VSS       | T17      | P17      |

| VSS       | T18      | P18      |

| SIGNAL | SiS5591  | SiS5592  |

|--------|----------|----------|

| NAME   | BALL NO. | BALL NO. |

| VSS    | U12      | N12      |

| VSS    | U13      | N13      |

| VSS    | U14      | N14      |

| VSS    | U16      | N16      |

| VSS    | U17      | N17      |

| VSS    | U18      | N18      |

| VSS    | V12      | M12      |

| VSS    | V13      | M13      |

| VSS    | V16      | M16      |

| VSS    | V17      | M17      |

| VSS    | V18      | M18      |

| VSSG   | D7       | AF7      |

| VSSG   | D8       | AF8      |

| VSSG   | D9       | AF9      |

| VSSG   | D20      | AF20     |

| VSSG   | D21      | AF21     |

| VSSG   | D22      | AF22     |

| VSSG   | E13      | AE13     |

| VSSG   | E14      | AE14     |

| VSSG   | F25      | AD25     |

| VSSG   | G4       | AC4      |

| VSSG   | AA4      | J4       |

| VSSG   | AC4      | G4       |

| VSSG   | AE18     | E18      |

| VSSG   | AE22     | E22      |

| VSSP   | Y3,      | K3       |

| W/R#   | AF28     | D28      |

### 4. PIN DESCRIPTIONS

### 4.1 SiS5591/5592 PIN DESCRIPTION

#### 4.1.1 Host Bus Interface

| SiS5591<br>BALL NO. | SiS5592<br>BALL NO. | NAME   | TYPE<br>ATTR | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|---------------------|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U29                 | N29                 | CPUCLK | I            | Host Clock :                                                                                                                                                                                                                                                                                                                                                     |

|                     |                     |        |              | Primary clock input to drive the part.                                                                                                                                                                                                                                                                                                                           |

| AE27                | E27                 | ADS#   | I            | Address Status :                                                                                                                                                                                                                                                                                                                                                 |

|                     |                     |        |              | Address Status is driven by the CPU to indicate the start of a CPU bus cycle.                                                                                                                                                                                                                                                                                    |

| AA26                | J26                 | M/IO#  | I            | Memory I/O Command Indicator :                                                                                                                                                                                                                                                                                                                                   |

|                     |                     |        |              | Memory I/O definition is an input to indicate an I/O cycle when low, or a memory cycle when high.                                                                                                                                                                                                                                                                |

| AE26                | E26                 | D/C#   | I            | Data/Code Command Indicator :                                                                                                                                                                                                                                                                                                                                    |

|                     |                     |        |              | Data/Code is used to indicate whether the current cycle is a data or code access.                                                                                                                                                                                                                                                                                |

| AF28                | D28                 | W/R#   | I            | Write/Read Command Indicator :                                                                                                                                                                                                                                                                                                                                   |

|                     |                     |        |              | Write/Read from the CPU indicates whether the current cycle is a write or read access.                                                                                                                                                                                                                                                                           |

| AA25                | J25                 | BRDY#  | О            | Burst Ready :                                                                                                                                                                                                                                                                                                                                                    |

|                     |                     |        |              | Burst Ready indicates that data presented are valid during a burst cycle.                                                                                                                                                                                                                                                                                        |

| AD28                | F28                 | CACHE# | I            | Cacheable Indicator :                                                                                                                                                                                                                                                                                                                                            |

|                     |                     |        |              | The Cache pin indicates an L1 internally cacheable read cycle or a burst write-back cycle. If this pin is driven inactive during a read cycle, the CPU will not cache the returned data, regardless of the state of the KEN# pin.                                                                                                                                |

| AD27                | F27                 | KEN#/  | О            | Cache Enable/Invalidate :                                                                                                                                                                                                                                                                                                                                        |

|                     |                     | INV    |              | This function as both the KEN# signal during CPU read cycles, and the INV signal during L1 snoop cycles. During CPU cycles, KEN/INV is normally low. KEN#/INV will be driven high during the 1st BRDY# or NA# assertion of a non-L1-cacheable CPU read.  KEN#/INV is driven high (low) during the EADS# assertion of a PCI master DRAM write (read) snoop cycle. |

| AD25                | F25                 | NA#    | О            | Next Address :                                                                                                                                                                                                                                                                                                                                                   |

|                     |                     |        |              | The SiS Chip always asserts NA# no matter the burst, or pipelined burst SRAMs are used. This signal is connected to CPU and indicate to CPU that it is ready to process a second cycle.                                                                                                                                                                          |

| AE29                     | E29                 | BOFF#     | О   | Back Off:                                                                                                                                                                                                                                                    |

|--------------------------|---------------------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                     |           |     | The SiS Chip asserts BOFF# to stop the current CPU                                                                                                                                                                                                           |

|                          |                     |           |     | cycle.                                                                                                                                                                                                                                                       |

| AD26                     | F26                 | AHOLD     | О   | Address Hold :                                                                                                                                                                                                                                               |

|                          |                     |           |     | The SiS Chip asserts AHOLD when a PCI master is performing a cycle to DRAM. AHOLD is held for the duration of PCI burst transfer. The SiS Chip negates AHOLD when the completion of PCI to DRAM read or write cycles complete and during PCI peer transfers. |

| AB26                     | H26                 | HLOCK#    | I   | Host Lock:                                                                                                                                                                                                                                                   |

|                          |                     |           |     | When CPU asserts HLOCK# to indicate the current bus cycle is locked.                                                                                                                                                                                         |

| AB25                     | H25                 | EADS#     | О   | External Address Strobe :                                                                                                                                                                                                                                    |

|                          |                     |           |     | The EADS# is driven to indicate that a valid external address has been driven to the CPU address pins to be used for an inquire cycle.                                                                                                                       |

| AF29                     | D29                 | HITM#     | I   | Hit Modified :                                                                                                                                                                                                                                               |

|                          |                     |           |     | Hit Modified indicates the snoop cycle hits a modified line in the L1 cache of the CPU.                                                                                                                                                                      |

| AE28                     | E28                 | SMIACT#   | I   | System Management Interrupt Active :                                                                                                                                                                                                                         |

|                          |                     |           |     | The SMIACT# pin is used as the SMI acknowledgement input from the CPU to indicate that the SMI# is being acknowledged and the processor is operating in System Management Mode (SMM).                                                                        |

| AG27,AF23,               | C27,D23,            | HBE[7:0]# | I   | Host Byte Enables :                                                                                                                                                                                                                                          |

| AH27,AC25,               | B27,G25,            |           |     | CPU Byte Enables indicate which byte lanes on the                                                                                                                                                                                                            |

| AG28,AF26,<br>,AC26,AF27 | C28,D26,<br>G26,D27 |           |     | CPU data bus carry valid data during the current bus cycle. HBE7# indicates that the most significant byte of the data bus is valid while HBE0# indicates that the least significant byte of the data bus is valid.                                          |

| AJ22,AF20,               | A22,D20,            | HA[31:3]  | I/O | Host Address Bus :                                                                                                                                                                                                                                           |

| AH23,AG23,               | B23,C23,            |           |     | The Host Address is driven by the CPU during CPU                                                                                                                                                                                                             |

| AJ21,AH22,               | A21,B22,            |           |     | bus cycles. The SiS Chip forwards it to either the                                                                                                                                                                                                           |

| AE20,AF19,               | E20,D19,            |           |     | DRAM or the PCI bus depending on the address range. The address bus is driven by the SiS Chip                                                                                                                                                                |

| AG21,AG22,               |                     |           |     | during bus master cycles or Flushing L2 cycle.                                                                                                                                                                                                               |

| AH21,AE23,               | B21,E23,            |           |     |                                                                                                                                                                                                                                                              |

|                          | A26,B26,            |           |     |                                                                                                                                                                                                                                                              |

|                          | C26,D22,            |           |     |                                                                                                                                                                                                                                                              |

|                          | B25,A25,            |           |     |                                                                                                                                                                                                                                                              |

| AG25,AF25,               |                     |           |     |                                                                                                                                                                                                                                                              |

|                          | A24,D21,            |           |     |                                                                                                                                                                                                                                                              |

|                          | E25,B24,            |           |     |                                                                                                                                                                                                                                                              |

|                          | D24,E21,            |           |     |                                                                                                                                                                                                                                                              |

| AG24,AE24,               | C24,E24,            |           |     |                                                                                                                                                                                                                                                              |

| AJ23                     | A23                 |           |     |                                                                                                                                                                                                                                                              |

| W26,Y29, | L26,K29,   | HD[63:0] | I/O | Host Data Bus :                                                                                                |

|----------|------------|----------|-----|----------------------------------------------------------------------------------------------------------------|

| W27,V25, | L27,M25,   |          |     | The Host data is driven by the CPU during CPU write                                                            |

| W28,W29, | L28,L29,   |          |     | cycle. The Host data is driven by L2 in three                                                                  |

| V27,V26, | M27,M26,   |          |     | conditions:                                                                                                    |

| V28,V29, | M28,M29,   |          |     | One is the CPU reads cycle and it hits the L2 cache.                                                           |

| U26,U28, | N26,N28,   |          |     | The other is the CPU reads cycle but the data does not exist in L2 cache, and it needs to perform a write-back |

| U27,T26, | N27,P26,   |          |     | cycle before a burst line fill. Another is the flushing                                                        |

| U25,T27, | N25,P27,   |          |     | L2 cycle. When CPU reading data from DRAM, the                                                                 |

| T28,R28, | P28,R28,   |          |     | Host data is driven by SiS5591/5592.                                                                           |

| T25,R27, | P25,R27,   |          |     |                                                                                                                |

| T29,P26, | P29,T26,   |          |     |                                                                                                                |

| R26,R29  | R26,R29,   |          |     |                                                                                                                |

| P25,P27, | T25,T27,   |          |     |                                                                                                                |

| P29,P29, | T29,T29,   |          |     |                                                                                                                |

| P28,N27, | T28,U27,   |          |     |                                                                                                                |

| N26,N29, | U26,U29,   |          |     |                                                                                                                |

| N28,N25, | U28,U25,   |          |     |                                                                                                                |

| M28,M27, | V28,V27,   |          |     |                                                                                                                |

| M25,L29, | V25,W29,   |          |     |                                                                                                                |

| L28,L27, | W28,W27,   |          |     |                                                                                                                |

| M26,L29, | V26,W29,   |          |     |                                                                                                                |

| L25,K28, | W25,Y28,   |          |     |                                                                                                                |

| K29,K27, | Y29,Y27,   |          |     |                                                                                                                |

| J29,J27, | AA29,AA27, |          |     |                                                                                                                |

| J28,L26, | AA28,W26,  |          |     |                                                                                                                |

| H28,H27, | AB28,AB27, |          |     |                                                                                                                |

| H29,K25, | AB29,Y25,  |          |     |                                                                                                                |

| G26,G27, | AC26,AC27, |          |     |                                                                                                                |

| K26,G28, | Y26,AC28,  |          |     |                                                                                                                |

| G29,F27, | AC29,AD27, |          |     |                                                                                                                |