#### Features:

- Single Chip 80386SX/286 PC/AT Compatible Solution for CPU Clock Speeds to 20MHz

- SX Mode or 286 Mode

- Supports up to 8 MB DRAM using 1M or 256K

Devices in by 1 or 4 configuration

- · Page Mode and 2 or 4-Way Interleaving

- LIM EMS 4.0 Support in Hardware using 2 Sets of 32 EMS Registers

- 8-Bit or 16-Bit BIOS Support

- · Asynchronous AT Bus Clock

- Supports up to 12 MHz Backplane Operation

- Programmable DRAM Timing

- Port 92 Alternate GATEA20 and Hot Reset

- Shadow RAM support over entire C0000-DFFFF range in 16K increments

- BIOS Shadow support in 64K increments

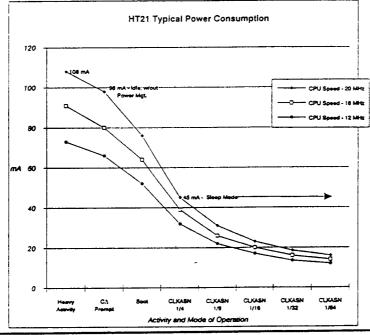

- Built-in Sleep Mode

- Three-state control pins for board level testing

- HCMOS Technology

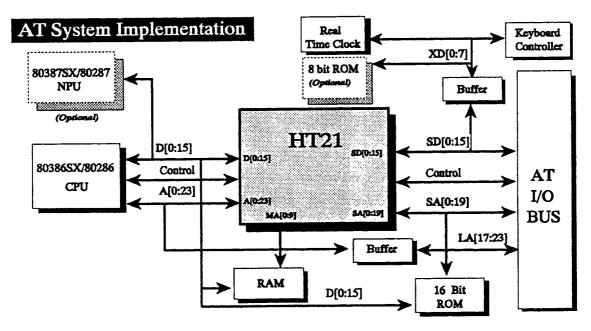

## Description

The HT21 is an advanced PC/AT compatible, singlechip 80386SX/80286 design solution. This highly integrated single chip allows simple, low cost system design options while featuring high performance, low power consumption, and minimum board space requirements. Advanced memory management features include support for page mode, 2 or 4-way interleaving in both pipelined and non-pipelined modes. The LIM 4.0 hardware implementation features dual sets of 32 registers with full context support for highest performance optimization of extended local memory accesses. An advanced EMS hardware write-protect option is provided. The HT21 supports 256K and 1M DRAMs in 1 by 1, 1 by 4, and 1 by 9 device configurations for up to 8MB of on-board system memory. A flexible Shadow RAM option for System and Video BIOS as well as 8-16-bit BIOS options adds to overall design versatility.

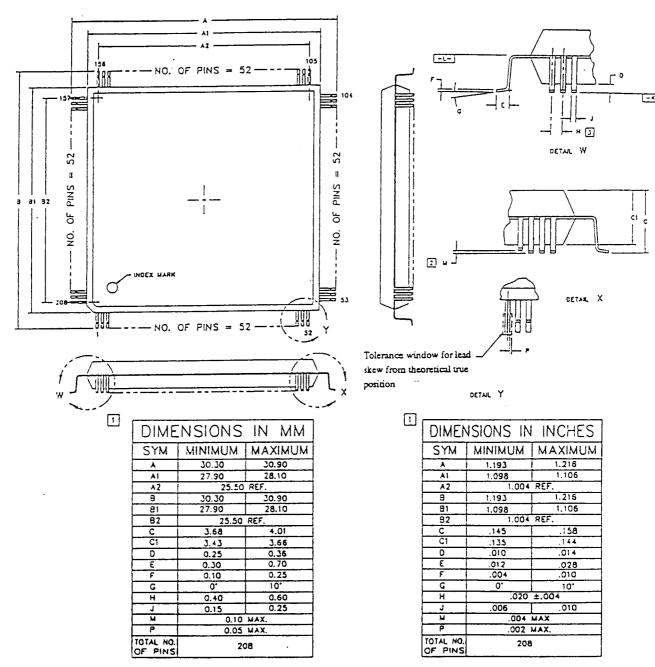

A complete PC/AT compatible system with advanced features may be implemented with minimal external support logic. The HT21 performs all CPU and peripheral support functions in a single chip. Integrated device functions include DMA Controllers, a Memory Mapper, Timers, Counters, Interrupt Controllers, a Bus Controller and all supporting circuitry for PC core logic requirements. The chip also contains all the necessary address buffers, data transceivers, memory drivers, parity checking and supporting circuitry for a complete high performance computer solution. An asynchronous AT Bus clock allows for a constant 8MHz Bus clock rate for highest bus device compatibility as defined in IEEE Spec P996. In controlled bus applications the HT21 supports up to a 12 MHz Bus Clock rate. This device is packaged in a 208-pin Plastic Quad Flat Pack combining several external buffers into this space saving solution.

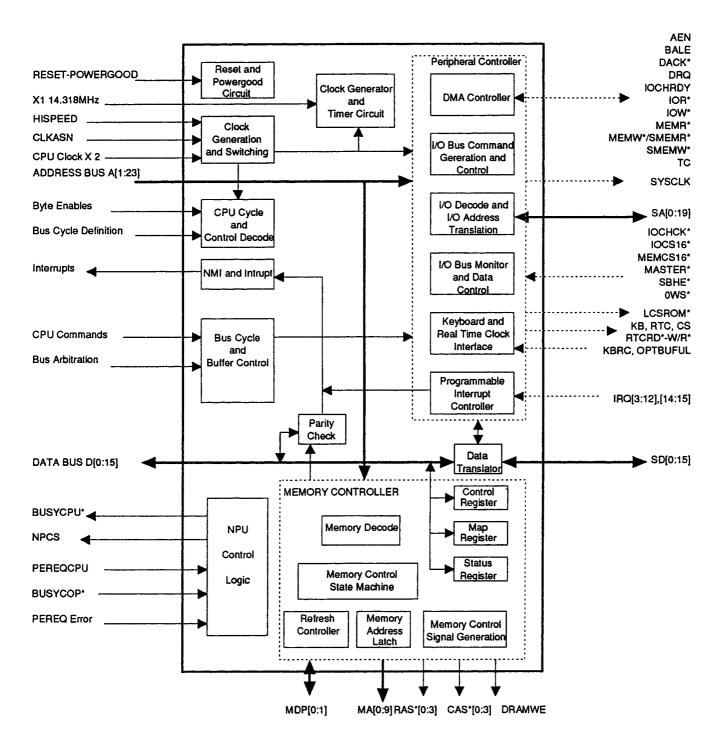

#### Overview:

The HT21 single chip, integrates the majority of the main board logic required for a cost effective, high performance PC AT-compatible computer based on either a 80286 or 80386SX microprocessor. It provides address control and buffering of the A, SA, and MA buses as well as providing necessary data path interface.

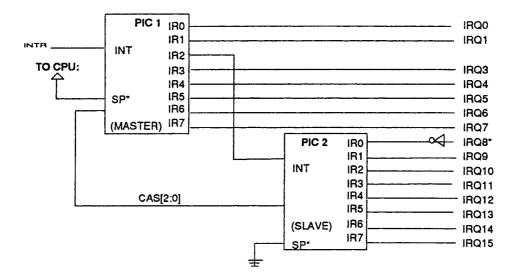

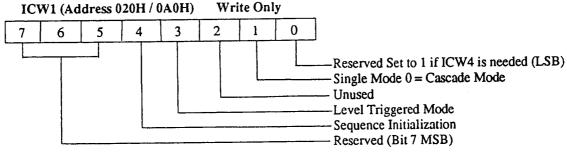

Peripheral circuit functions embedded in this device include: an 82284 compatible clock generation and READY interface, 82288 compatible bus controller, 74612 compatible memory mapper, 8254 compatible programmable interval timer, two 8237 compatible DMA controllers, and two 8259 compatible interrupt controllers.

Additional feature enhancements incorporated into the chip are power management sleep mode, high performance hardware LIM EMS control, 8-bit or 16-bit wide BIOS options, flexible memory options, OS/2 fast alternate gate A20 and hot reset. This section of the data sheet provides functional descriptions of the following logic sections of the HT21:

- CPU Interface

- Clock Generation

- Internal Clocks

- Clock Switching Logic

- I/O Channel Interface

- I/O Bus

- I/O Decode

- I/O Address Map

- Keyboard Controller Interface

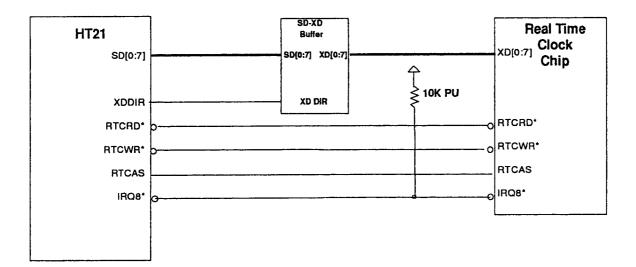

- Real-Time Clock Interface

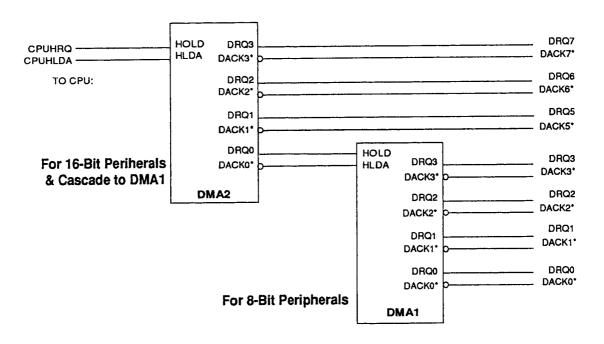

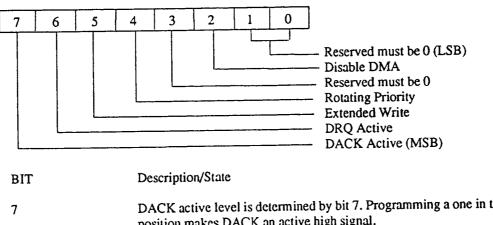

- DMA Controller

- Address Generation

- Register Descriptions

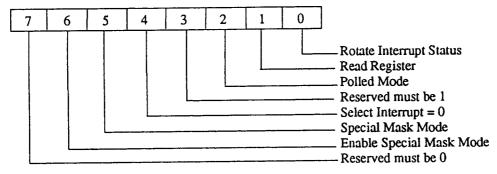

- Interrupt Controller

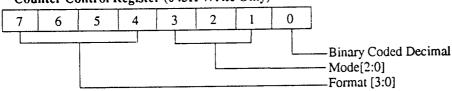

- Programmable Interval Timer

- Bus Control

- NPU Interface

- Power Management / Sleep mode

- System Control Port Port 92H

- Memory Controller

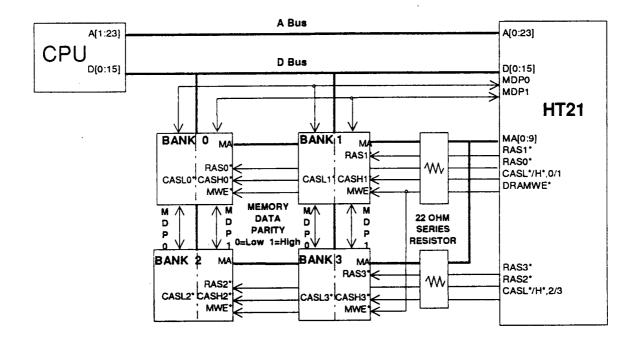

- DRAM Interface

- Extended Memory

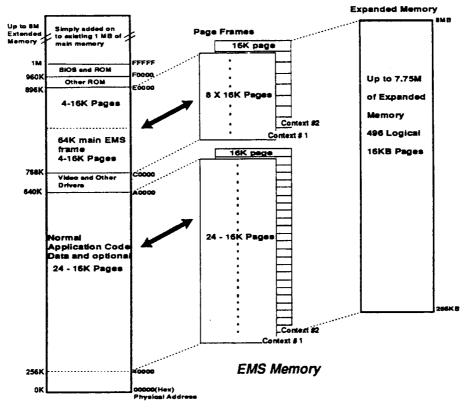

- EMS

- ROM/BIOS Interface

- Pipeline Option

Internal Block Diagram

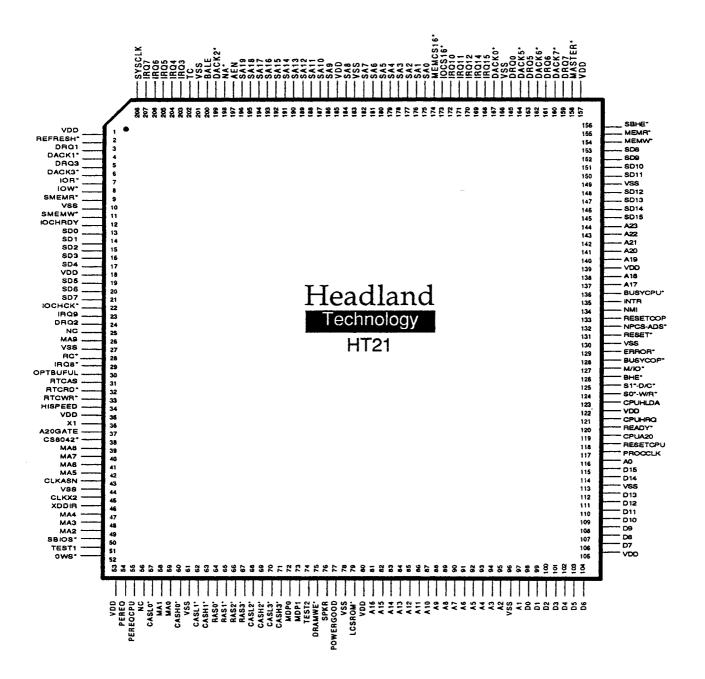

# Pin Names and Numbers in Alphabetical Order

|                   |                                   | DOMES ACC. | 77                          |

|-------------------|-----------------------------------|------------|-----------------------------|

| A[0:23]           | 116, 97, 95-81, 137, 138, 140-144 | POWERGOOD  | 77                          |

| A20GATE           | 37                                | PROCCLK    | 117                         |

| AEN               | 197                               | RAS*[0:3]  | 64-67                       |

| BHE*              | 126                               | RC*        | 28                          |

| BALE              | 200                               | READY*     | 120                         |

| BUSYCOP*          | 128                               | REFRESH*   | 2                           |

| BUSYCPU*          | 136                               | RESET*     | 131                         |

| CASH*[0:3]        | 60, 63, 69, 71                    | RESETCOP   | 133                         |

| CASL*[0:3]        | 57, 62, 68, 70                    | RESETCPU   | 118                         |

| CLKASN            | 43                                | RTCAS      | 31                          |

| CLKX2             | 45                                | RTCRD*     | 32                          |

| CPUA20            | 119                               | RTCWR*     | 33                          |

| CPUHLDA           | 123                               | S0*-W/R*   | 124                         |

| CPUHRQ            | 121                               | S1*-D/C*   | 125                         |

| CS8042*           | 38                                | SA[0:19]   | 175-182,184,186-196         |

| D[0:15]           | 98-104, 106-112, 114-115          | SBHE*      | 156                         |

| DACK*[0:3], [5:7] | 167,4,199,6,164,162,160           | SBIOS*     | 50                          |

| DRAMWE*           | 75                                | SD[0:15]   | 13-17,19-21,153-150,        |

| DRQ[0:3], [5:7]   | 165,3,24,5,163,161,159            |            | 148-145                     |

| ERROR*            | 129                               | SMEMR*     | 9                           |

| HISPEED           | 34                                | SMEMW*     | 11                          |

| INTR              | 135                               | SPKR       | 76                          |

| IOCHCK*           | 22                                | SYSCLK     | 208                         |

| IOCHRDY           | 12                                | TC         | 202                         |

| IOCS16*           | 173                               | TEST[1:2]  | 51, 74                      |

| IOR*              | 7                                 | X1         | <b>36</b>                   |

| IOW*              | 8                                 | XDDIR      | 46                          |

| IRQ[3:7]          | 203-207                           | 0WS*       | 52                          |

| IRQ8*             | 29                                | GND        | 10,27,44,61,78,96,113,      |

| IRQ[9:12]         | 23, 172-170                       |            | 130,149,166,183,201         |

| IRQ[14:15]        | 169, 168                          | VCC        | 1, 18, 35, 53, 80, 105, 122 |

| LCSROM*           | 79                                |            | 139,157,185                 |

| M/IO*             | 127                               |            |                             |

| MA[0:9]           | 59, 58, 49-47, 42-39,26           |            |                             |

| MASTER*           | 158                               |            |                             |

| MDP[0:1]          | 72-73                             |            |                             |

| MEMCS16*          | 174                               |            |                             |

| MEMR*             | 155                               |            |                             |

| MEMW*             | 154                               |            |                             |

| NA*               | 198                               |            |                             |

| NC                | 25, 56                            |            |                             |

| NMI               | 134                               |            |                             |

| NPCS*-ADS*        | 132                               |            |                             |

| OPTBUFUL          | 30                                |            |                             |

| PEREQ             | 54                                |            |                             |

| PEREQCPU          | 55                                |            |                             |

| TEREVELO          | <i>33</i>                         |            |                             |

| Pin<br>Symbol        | Pin<br>Number            | Pin<br>Type | Internal<br>Pull<br>Up/Dn | Description                                                                                                                                                                                                                                                                                              |

|----------------------|--------------------------|-------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU In               | terface 2                | 86 or       | 386SX                     | Mode                                                                                                                                                                                                                                                                                                     |

| A[0:16]              | 116,97,95-81             | I           | PU                        | Address bits [0:16]: Inputs from 80286 CPU or 80386SX CPU. The HT21 takes the address bus inputs and generates SA bus for I/O slots, and the MA bus for the system DRAM.                                                                                                                                 |

| A[17:19],<br>[21:23] | 137-138,140,<br>142-144  | I/O         | PU                        | A[17:19], [21:23], bi-directional Address lines: Inputs from [21:23] the 80286 CPU or 80386SX CPU used for memory selection decoding. They output addresses from the memory mapper (internal) logic during DMA operations.                                                                               |

| A20                  | 141                      | I/O         |                           | Address 20 is output for CPU cycles and input during Bus Master cycles.                                                                                                                                                                                                                                  |

| ADS* (NPCS*)         | 132                      | I/O         | PU                        | Multiplexed ADS* or NPCS* operations, depending on auto-sense definition of mode. 386SX Mode Input ADS*, when 386SX mode is selected (Mode=0). ADS*: ADdress Status input from the 386SX. When low, the 386SX is providing valid address on A[23:1], and driving the R/W*, D/C*, M/IO*, BHE*, A0 control |

| <b>(</b> ,           |                          |             |                           | lines.                                                                                                                                                                                                                                                                                                   |

| BHE*                 | 126                      | I           | PU                        | Byte High Enable: A low at this input enables the high byte [15:8] of the data bus. Driven by the CPU.                                                                                                                                                                                                   |

| CPUA20               | 119                      | I           | PU                        | CPU Address 20 from CPU: This input drives the A20 output pin, if CPUHLDA = 0 and A20GATE = 1.                                                                                                                                                                                                           |

| CPUHLD               | A 123                    | Ī           | PD                        | CPU Hold Acknowledge: The CPU drives this input high to indicate that it has released control of the buses.                                                                                                                                                                                              |

| CPUHRQ               | 121                      | 0           |                           | CPU Hold ReQuest: When high, the HT21 needs to perform a DMA, Refresh, or bus Master operation.                                                                                                                                                                                                          |

| D[0:15]              | 98-104,<br>106-112, 114- | I/O<br>115  | PU                        | Bi-directional Data Bus: Transfering data to/from the CPU. This is part of what is commonly referred to as the Local Bus.                                                                                                                                                                                |

| D/C*                 | 125                      | I           | PU                        | Multiplexes D/C* or S1* functions, depending on auto-sense mode selection. Input D/C*, when 386SX support (mode = 0). D/C*: Data or Control bus cycles. A high level indicates a 386SX Mode Memory or I/O Data cycle by the 386SX. Low indicates a control                                               |

| (S1*)                |                          |             |                           | cycle; inclusively interrupt acknowledge, halt, or code fetches.                                                                                                                                                                                                                                         |

| Pin<br>Symbol | Pin<br>Number | Pin<br>Type | Internal<br>Pull<br>Up/Dn | Description                                                                                                                                                                                                                                                                                             |

|---------------|---------------|-------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTR          | 135           | O           |                           | INTerrupt Request: A high on this output requests an interrupt from the CPU.                                                                                                                                                                                                                            |

| M/IO*         | 127           | I           | PU                        | Memory I/O: From CPU: if high during set up, memory cycle is in progress; if low, I/O cycle is occuring. Three-state when the CPU is in Hold Acknowledge. (See CPUHLDA)                                                                                                                                 |

| NMI           | 134           | 0           |                           | Non-Maskable Interrupt: A high level forces the CPU to unconditionally execute an interrupt routine.                                                                                                                                                                                                    |

| PROCCLK       | 117           | 0           |                           | PROCessor CLock: this output supplies the clock signal for the CPU and co-processor. It drives CLK on the CPU, and the clock lines on the co-processor. Rate determined by HISPEED.                                                                                                                     |

| READY*        | 120           | 0           |                           | READY: A low level tells the CPU that the current bus cycle is near completion.                                                                                                                                                                                                                         |

| RESETCPU      | J 118         | 0           |                           | RESET CPU: A low-to-high transition resets the CPU during powerup, keyboard reset, and shutdown status. The rising edge resets the CPU, if the pin is held high for 16 clock cycles.                                                                                                                    |

| S0* (W/R*)    | 124           | I           | PU                        | Multiplexes S0* or W/R* functions, depending on auto-sense mode selection. Input S0* when 286 operation (mode = 1). 286 CPU Status bit. When S0*, S1*, INTA are low and M/IO* 286 Mode is high - a shutdown or halt of the 286 occurs. If A1 = 1, the CPU shuts down. If A1 = 0, the system shuts down. |

| S1*<br>(D/C*) | 125           | Ĭ           | PU                        | Multiplexes S1* or D/C* functions, depending on auto-sense mode selection. Input S1* when 286 operation (mode = 1). 286 Mode 286 CPU Status bit. (See S0*-W/R*)                                                                                                                                         |

| W/R* (S0*)    | 124           | I           | PU                        | Multiplexes W/R* or S0* functions, depending on auto-sense mode selection. Input W/R*, when 386SX support (mode = 0). W/R*: Write or Read bus cycles of the 386SX high for 386SX Mode Writes, low for Reads.                                                                                            |

| Pin<br>Symbol | Pin<br>Number | Pin<br>Type | Internal<br>Pull<br>Up/Dn | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|---------------|-------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

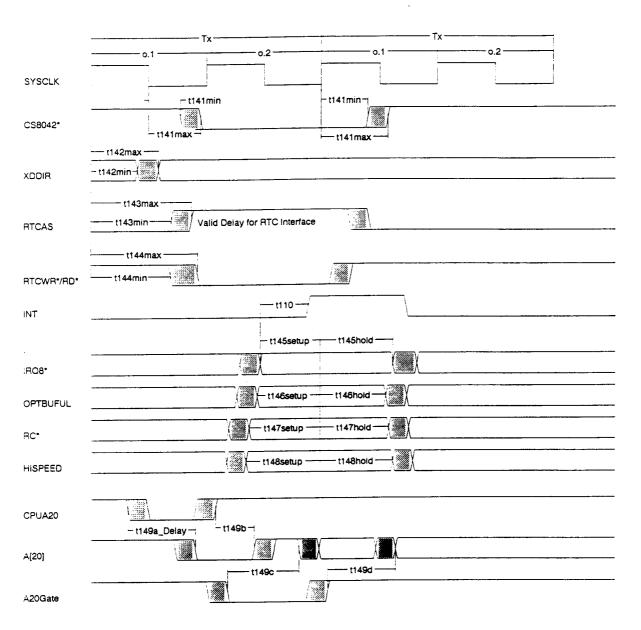

| Keyboar       | d and R       | TC I        | nterfac                   | e                                                                                                                                                                                                                                                                                                                                                                                                                            |

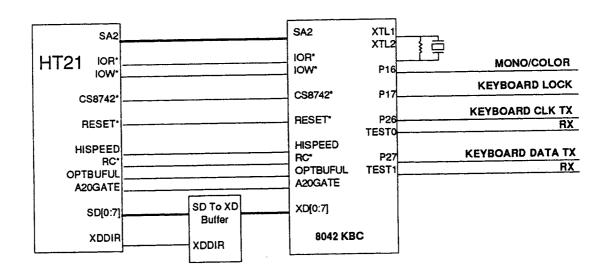

| CS8042*       | 38            | 0           |                           | Chip Select 8042: A low level drives CS* of an external keyboard controller.                                                                                                                                                                                                                                                                                                                                                 |

| IRQ8*         | 29            | I           | PU                        | This input is driven by a Real Time Clock interrupt output to support standard RTC devices. (Note that Interrupt Request 8 is active low, unlike the other Interrupt Requests.)                                                                                                                                                                                                                                              |

| OPTBUFUL      | . 30          | I           | PD                        | OutPuT BUffer FULl: Input from P24 of the keyboard controller. Setting this pin high activates the internal IRQ. This causes an INTR to the CPU, indicating the keyboard buffer is full.                                                                                                                                                                                                                                     |

| RC*           | 28            | I           | PU                        | Reset CPU: When driven low by the keyboard controller (P20), the CPU resets its internal registers.                                                                                                                                                                                                                                                                                                                          |

| RTCAS         | 31            | 0           |                           | Real Time Clock Address Strobe: A low to high signal transition latches the RAM address for read/write operations.                                                                                                                                                                                                                                                                                                           |

| RTCRD*        | 32            | 0           |                           | Real Time Clock ReaD: When low, data is read from the RTC.                                                                                                                                                                                                                                                                                                                                                                   |

| RTCWR*        | 33            | 0           |                           | Real Time Clock WRite: When low, data is written to the RTC.                                                                                                                                                                                                                                                                                                                                                                 |

| I/O Inte      | rface         |             |                           |                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AEN           | 197           | Ο           |                           | Address ENable DMA: This signal is used to disconnect the microprocessor and other devices from the I/O channel to allow DMA transfers to take place. When AEN is high, the DMA controller drives the address bus, data bus, I/O read/write lines and memory read/write signals.                                                                                                                                             |

| BALE          | 200           | 0           |                           | Buffered Address Latch Enable: This signal is provided by the 82288 bus controller and is used to latch valid addresses and memory decodes from the microprocessor. It is used by the I/O channel as an indicator of a valid microprocessor or DMA address (when used with AEN). A high level indicates the presence of valid address at the I/O slots. System Addresses (SA[0:19]) are latched on the falling edge of BALE. |

| Pin<br>Symbol                         | Pin<br>Number                          | Pin<br>Type | Internal<br>Pull<br>Up/Dn |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|----------------------------------------|-------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DACK*[0::<br>DACK*[5:                 |                                        | O<br>)      |                           | DMA ACKnowledge: When low, these signals are used to DACK*[5:7] requests (DRQ[0:3],[5:7]) from peripherals on the I/O expansion slots.                                                                                                                                                                                                                                                                                                                                                                               |

|                                       | 165, 3, 24, 5<br>163,161,159           |             | PD                        | DMA ReQuests: These asynchronous channel requests DRQ[5:7] are used by peripheral devices and the I/O channel microprocessors, active high signals request DMA services or control of the system. They are prioritized with DRQ0 having the highest priority and DRQ7 having the lowest. Each signal should be held high until the corresponding DMA Request Acknowledge (DACK* signal) goes active (low). DRQ[0:3] govern 8-bit DMA transfers, DRQ[5:7] control 16-bit DMA transfers with devices on the I/O slots. |

| IOCHCK*                               | 22                                     | I           | PU                        | I/O CHannel Check: A low on this input indicates there is an uncorrectable system error. Provides the system board with parity (error) information about memory or devices on the I/O channel. This causes the NMI (Non-Maskable Interrupt) output to become active (high), and interrupts the CPU. Needs external 4.7K Ohm pullup.                                                                                                                                                                                  |

| IOCHRDY                               | 12                                     | I           | PU                        | I/O CHannel ReaDY: This signal is used by any slow I/O device driving this line low immediately upon detecting its valid address and a Read/Write command. The HT21 will add more wait states for a page miss by pulling this signal low. Needs external 1K Ohm pullup and should be driven low or active by any open collector device.                                                                                                                                                                              |

| IOCS16*                               | 173                                    | I           | PU                        | I/O Chip Select 16: A low indicates a 16-bit I/O data transfer on the SA bus. This signal should be driven by an open collector or three-state driver capable of sinking 20mA. Needs external 300 Ohm pullup.                                                                                                                                                                                                                                                                                                        |

| IOR*                                  | 7                                      | I/O         | PU                        | I/O Read: When low, instructs an I/O device to drive or write its data onto the data bus. It is driven by the microporcessor or DMA controller, either resident in the system or on the I/O channel.                                                                                                                                                                                                                                                                                                                 |

| IOW*                                  | 8                                      | I/O         | PU                        | I/O Write: When low, instructs an I/O device to read or capture the data on the data bus. It may be driven by any microprocessor or DMA controller in the system.                                                                                                                                                                                                                                                                                                                                                    |

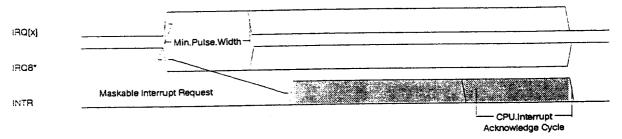

| IRQ[3:7],<br>IRQ[9:12],<br>IRQ[14:15] | 203-207,<br>23,<br>172-170,<br>169-168 | Ī           | PU                        | Interrupt ReQuest: These pins signal the microprocessor that an I/O device needs attention. An interrupt request is generated when an IRQ line is raised from low to high. The line must be held high until the microprocessor acknowledges the interrupt request (Interrupt Service routine). IRQ3 has the highest priority interrupt, IRQ15 the lowest.                                                                                                                                                            |

| Pin<br>Symbol | Pin<br>Number | Pin<br>Type | Internal<br>Pull<br>Up/Dn | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---------------|-------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MASTER*       | 158           | I           | PU                        | MASTER*: This signal is used with a DRQ line to gain control of the system. A processor or DMA controller on the I/O channel issues a DRQ to a DMA channel in cascade mode and receives a DACK*. Upon receiving the DACK*, an I/O microprocessor pulls MASTER* input low, which will allow it to control the system address, data, and control lines. After this signal is pulled low the I/O microprocessor must wait one system clock period before driving the address and data lines and two clock periods before issuing a Read/Write command. If this signal is held low for more than 15 microseconds, the system memory may be lost because of a lack of refresh. |

| MEMCS16*      | 174           | Ī           | PU                        | MEMory Chip Select 16 wide: External devices drive this input low for 16-bit data transfers. Connects to the system expansion bus. Needs external 300 Ohm pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MEMR*         | 155           | I/O         | PU                        | MEMory Read signal: Output is low during a memory read cycle. This signal instructs the memory devices to drive data onto the data bus. It can be driven by any microprocessor or DMA controller in the system. When a microprocessor on the I/O channel drives this signal it must have the address lines valid on the bus for 1 system clock period before driving MEMR* active. Three-stated when MASTER* is low and the CPU does not control the system. Not active during local memory cycles.                                                                                                                                                                       |

| MEMW*         | 154           | I/O         | PU                        | MEMory Write signal:Output is low during a memory write. This signal instructs the memory devices to store the data present on the data bus. It is active during all memory write cycles and can be driven by any microprocessor or DMA controller in the system. When driven by a microprocessor on the I/O channel the address lines on the bus must be valid for one system clock period before driving the signal active. This is three-stated when MASTER is low. Not active in local memory cycles.                                                                                                                                                                 |

| REFRESH*      | 2             | I/O         |                           | REFRESH input is low when the current cycle is for memory refresh and can be driven by a microprocessor on the I/O channel. Needs external 470 Ohm pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SAO           | 175           | I/O         | PU                        | System Address bit 0: Bi-directional address bit on the expansion slot. It supplies address bit 0 during refreshes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pin<br>Symbol | Pin<br>Number                        | Pin<br>Type | Internal<br>Pull<br>Up/Dn | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|--------------------------------------|-------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SA[1:19]      | 176-182,184,<br>186-196              | I/O         | PU                        | System Address bus: Bi-directional bus used to address memory and I/O devices within the system. These lines alone allow access of up to 1MB of memory and up to 16MB when used with LA[18:23]. SA[0:19] are gated on the system bus when BALE is high and are latched on the falling edge of BALE. These signals are generated by the microprocessor or DMA controller. They also may be driven by other microprocessors or DMA controllers that reside on the I/O channel.                                                    |

| SBHE*         | 156                                  | I/O         | PU                        | System Byte High Enable: Low when peripherals are performing a transfer on the upper byte. 16-bit devices use SBHE* to condition data bus buffers tied to SD[8:15].                                                                                                                                                                                                                                                                                                                                                             |

| SD[0:15]      | 13-17,19-21,<br>153-150,<br>148-145, | I/O         | PU                        | I/O System Data Bus: These signals provide bus bits [0:15] for the microprocessor, memory, and I/O devices. SD0 is the least-significant bit and SD15 is the most significant bit. All 8-bit devices on the I/O channel use SD[0:7] for communications to the microprocessor. The 16-bit devices will use SD[0:15]. To support 8-bit devices, the data on SD[8:15] will be gated to SD[0:7] during 8-bit transfers to these devices; 16-bit microprocessor transfers to 8-bit devices will be converted to two 8-bit transfers. |

| SMEMR*        | 9                                    | 0           | ,                         | System MEMory Read: Low during memory reads. This signal instructs the memory devices to drive data onto the data bus. It is active only when the memory decode is within the low 1MB of memory space. This is a buffered version of MEMR*.                                                                                                                                                                                                                                                                                     |

| SMEMW*        | * 11                                 | 0           |                           | System MEMory Write: Low during memory writes. This signal instructs the memory devices to store the data present on the data bus. It is active only when the memory decode is within the low 1 MB of memory space. This is a buffered version of MEMW*.                                                                                                                                                                                                                                                                        |

| SYSCLK        | 208                                  | 0           |                           | SYStem CLock: This provides a clock for devices on the expansion slot. SYSCLK is a quarter of CLKASN.                                                                                                                                                                                                                                                                                                                                                                                                                           |

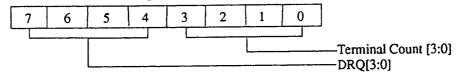

| TC            | 202                                  | 0           |                           | Terminal Count: pulses high when the DMA channel terminal count is reached. This signal is available on the expansion slots.                                                                                                                                                                                                                                                                                                                                                                                                    |

| XDDIR         | 46                                   | 0           |                           | External Data BUS control for KBD and RTC, SBIOS: 1 = Write 0 = Read                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pin<br>Symbol | Pin<br>Number | Pin<br>Type | Internal<br>Pull<br>Up/Dn | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|---------------|---------------|-------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ows*          | 52 I          |             | PU                        | Zero Wait State: This signal tells the microprocesser that it complete the present bus cycle without inserting additional way cycles. It comes from an address decode gated with a Read/Write command. In order to run a memory cycle to an 8-bit device with a minimum of 2 wait states, 0WS* must be driven low one syste clock after Read/Write commands are gated with the address decode for the device. These Read/Write commands are active the falling edge of the system clock. This signal should be drived by an open collector or three-state driver capable of sinking 20m External 300 Ohm pull up. |  |  |  |  |

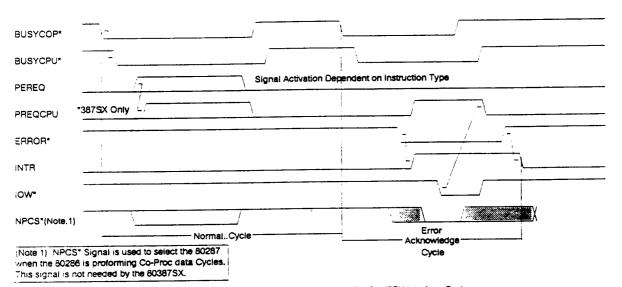

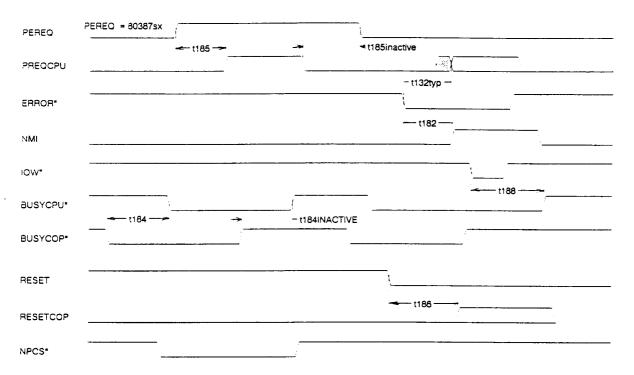

| NPU Int       | erface        |             |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| BUSYCOP*      | 128           | I           | PU                        | BUSYCOP* input to be connected to BUSY* output of the coprocessor. When the math co-processor is working, it drives this pin low, which in turn forces BUSYCPU* output low and halts the CPU.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| BUSYCPU*      | 136           | 0           |                           | BUSYCPU* output connects to the BUSY* input of the CPU. A low level on this pin indicates the math co-processor is operating. Interrupts are honored by the CPU while this input is low. (See ERROR*)                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| ERROR*        | 129           | I           | PU                        | ERROR: Connect ERROR* from the co-processor to this input. A low level indicates the math co-processor has an unmasked error condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| NPCS*         | 132           | I/O         | PU                        | Multiplexed NPCS* and ADS* operations, depending on autosense definition of mode. 286 Mode Output NPCS*, when 286 operation is selected (Mode=1). NPCS*: Numeric Processor Chip Select. A low output enables the co-processor chip.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| PEREQ         | 54            | I           |                           | Processor Extension REQuest: Request from NPU for Processor Extension. If this logic is to remain dormant leave this pin floating. This feature starts with Rev.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| PEREQCPU      | J 55          | 0           |                           | Processor Extension REQuest to CPU: Request passed on to CPU from NPU for extension. If this logic is to remain dormant leave this pin floating. This feature is implimented starting with Rev. C.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RESETCO       | P 133         | 0           |                           | RESET COP: A high signal resets the co-processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

12

| Pin<br>Symbol | Pin<br>Number                 | Pin<br>Type | Internal<br>Pull<br>Up/Dn | Description                                                                                                                                                                                                                          |

|---------------|-------------------------------|-------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

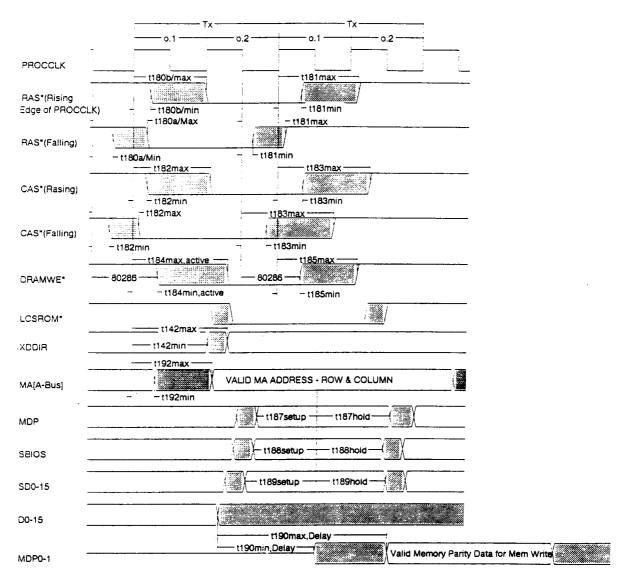

| Memory        | Interfa                       | ce          |                           |                                                                                                                                                                                                                                      |

| CASH*[0:3]    | 60,63,<br>69,71               | O           |                           | Column Address Strobe High order byte: Control up to four banks of DRAMs. These signals can be connected directly to DRAM CAS inputs through a 22 Ohm resistor. (Resistor value may vary with board layout and number of RAMs used.) |

| CASL*[0:3]    | 57,62,<br>68,70               | O           |                           | Column Address Strobe Low order byte: Controls up to four banks of DRAMs. These signals can be connected directly to DRAM CAS inputs through a 22 Ohm resistor. (Resistor value may vary with board layout and number of RAMs used.) |

| DRAMWE*       | 75                            | 0           |                           | DRAM Write Enable: Generates the write strobe to DRAMs. This is a gated signal derived from the MEMW* input.                                                                                                                         |

| LCSROM*       | 79                            | 0           |                           | Latch Chip Select ROM: Drives the chip enable pins of the EPROM, ie E0000-FFFFF and FE0000-FFFFFF for EPROMs.                                                                                                                        |

| MA[0:9]       | 59-58,<br>49-47,<br>42-39, 26 | 0           |                           | Multiplexed Address bus: to DRAMs, should connect to the memory address of the DRAM through 22 Ohm resistors.                                                                                                                        |

| MDP[0:1]      | 72-73                         | I/O         | PU                        | Memory Data Parity: Low (0) and high (1) bytes: When data is written to RAM or read from RAM its parity value is calculated.                                                                                                         |

| RAS*[0:3]     | 64-67                         | 0           |                           | Row Address Strobe: Controls up to four banks of DRAMs. These signals can be connected directly to DRAM RAS inputs through a 22 Ohm resistor. (Resistor value may vary with board layout and number of RAMs used.)                   |

| Clock In      | puts                          |             |                           |                                                                                                                                                                                                                                      |

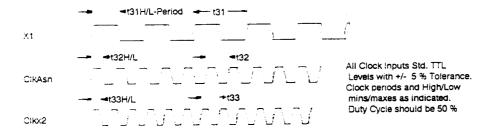

| CLKX2         | 45                            | I           | PU                        | CLock X 2: Drive this clock input at twice the desired processor clock (PROCCLK) frequency. This signal is used when CPU is running at "High" speed. For 16MHz system operations CLKX2 and CLKASN can share the 32MHz OSC.           |

| CLKASN        | 43                            | I           | PU                        | CLockASN: Drive this clock input at four times the desired SYSCLK frequency. This signal is used when CPU is running at "Low" speed. For 16MHz system operations CLKX2 and CLKASN can share the 32 MHz OSC.                          |

| X1            | 36                            | I           | PU                        | This input is tied to a 14.31818 MHz Oscillator, to generate OSC.                                                                                                                                                                    |

| Pin<br>Symbol  | Pin<br>Number | Pin<br>Type | Internal<br>Pull<br>Up/Dn | Description                                                                                                                                                                                                                   |

|----------------|---------------|-------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Miscella       | neous a       | nd Re       | set                       |                                                                                                                                                                                                                               |

| A20GATE        | 37            | I           |                           | Gates address from CPU: If CPUHLDA=0 the CPU is driving the address bus. When A20GATE is high, the upper address bit (CPUA20 input) drives the A20 pin directly, when low the A20 output is forced low if Port 92 bit $1=0$ . |

| HISPEED        | 34            | I           | PU                        | HIgh SPEED: When high, PROCCLK (the processor clock) speed is equal to the CLKX2 rate for on-board memory accesses. When low, PROCCLK is one half of CLKASN.                                                                  |

| NA*            | 198           | I           |                           | Next Address: This is used to place the HT21 in pipeline mode. A low or 0 = Pipeline mode, 1 = non-pipeline mode (default) must = 1 for 80286 operation.                                                                      |

| NC             | 25, 56        |             |                           | Not Connected: Reserved for future enhancements.                                                                                                                                                                              |

| POWER-<br>GOOD | 77            | I           | PU                        | POWERGOOD: When low, it resets the HT21 controller. A Schmitt Trigger buffers the input pin.                                                                                                                                  |

| RESET*         | 131           | 0           |                           | RESET: A low level used to reset the system logic at power-up or low-line voltage. (Open Drain Outputs)                                                                                                                       |

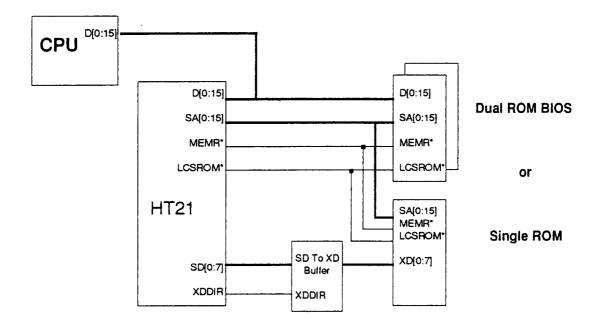

| SBIOS*         | 50            | I           | PU                        | Switch for single BIOS: 1 = Two Chip BIOS 0 = Single BIOS                                                                                                                                                                     |

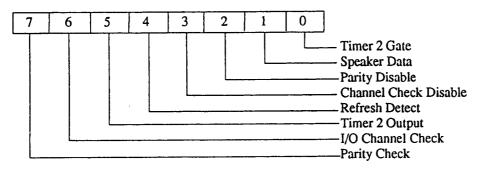

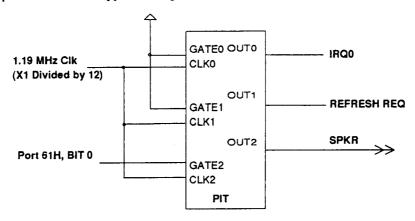

| SPKR           | 76            | 0           |                           | SPeaKeR: Output of the Timer 8254 Channel 2 (mega function) This connects to a speaker, through a buffer.                                                                                                                     |

| TEST [1:2]     | 51,74         | I           | PU                        | Tie TEST[1:2] ICT test functions can use these pins to float all output pins by pulling them low. For normal non-test operation these pins should not be used or connected.                                                   |

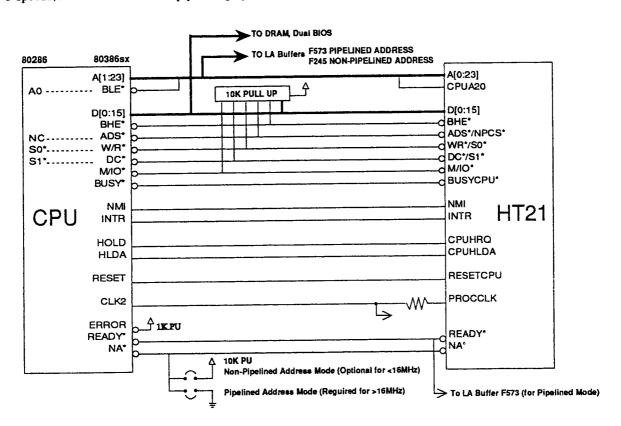

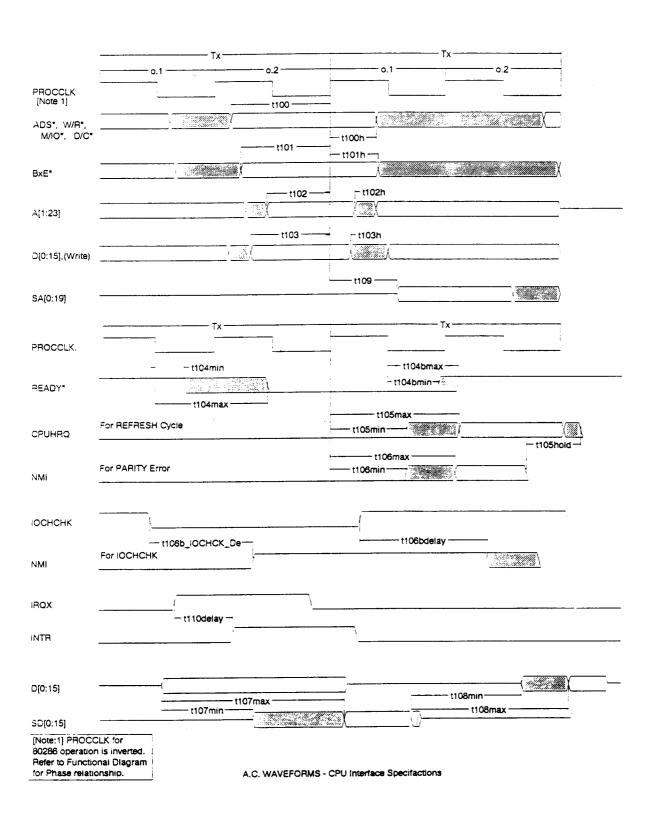

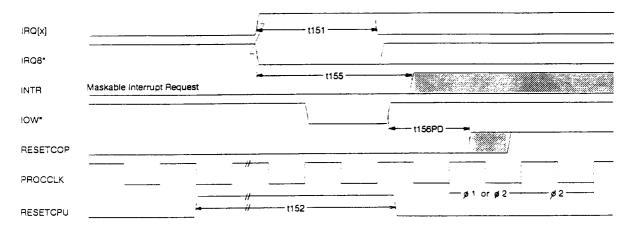

#### **CPU Interface**

The HT21 has built-in CPU auto mode select capability to provide either an 80286 or 80386SX microprocessor interface. This auto mode select is employed during reset by monitoring the default reset condition of multiplexed input pin used for S0\* signal input for 80286 CPU configuration or W/R signal input when used with 80386SX CPU configuration.

A high level on the S0\*-W/R\* pin would indicate the reset condition for the 80286 CPU and set the mode for 286 operation. A low level would indicate the reset condition for the 80386SX CPU and set the mode for 386SX operation. This mode select feature determines the signal interface and timing requirements for both 286 or 386SX CPU interface.

Both modes provide all the CPU main board interface signals for Numeric processor, memory, peripherals, and I/O interface required for a PC AT-compatible computer. The HT21 supports common CPU system clocks of 12.5, 16 and 20 MHz. To obtain the highest system performance with lower cost DRAM technology at higher CPU speeds, the 80386SX address pipelining option is fully supported.

CPU Interface Diagram

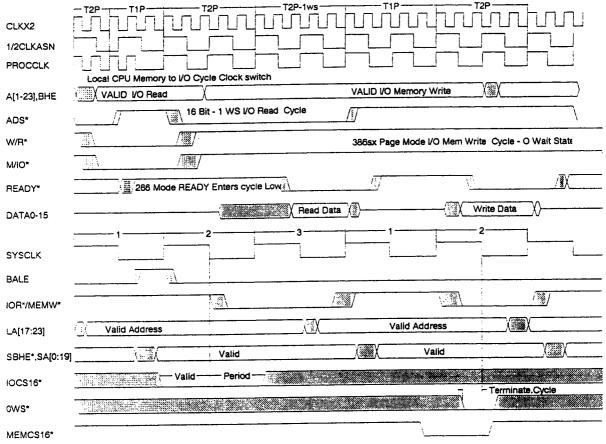

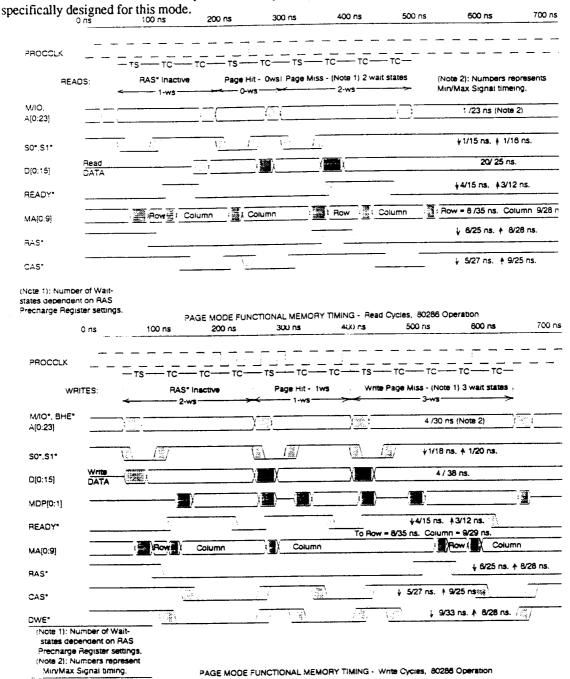

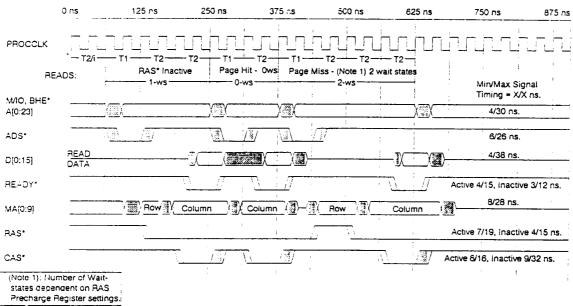

Major signal timing relationships and sequences are shown for both 80286 and 80386SX CPU interfaces. Both pipelined and non-pipelined address timings are shown for 80386SX CPU's with emphasis on the functional timing relationship between signals.

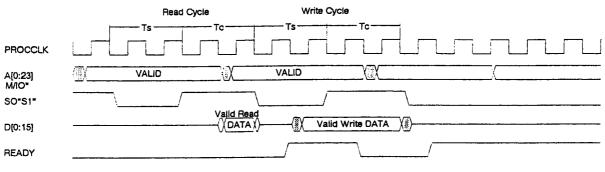

The following diagram illustrates a sample 80286 read and write cycle to memory or I/O address space. For more detailed CPU cycles and sequences please refer to the CPU manufacturers 80286 Data Sheet.

80286 CPU FUNCTIONAL TIMING - Read and Write Cycles

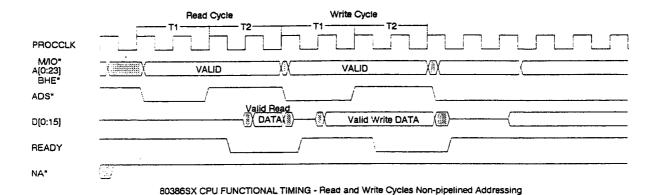

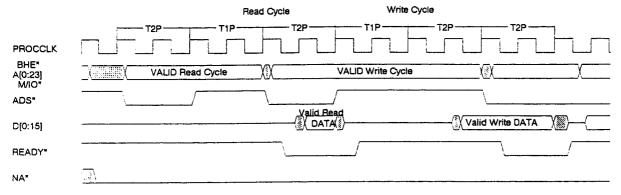

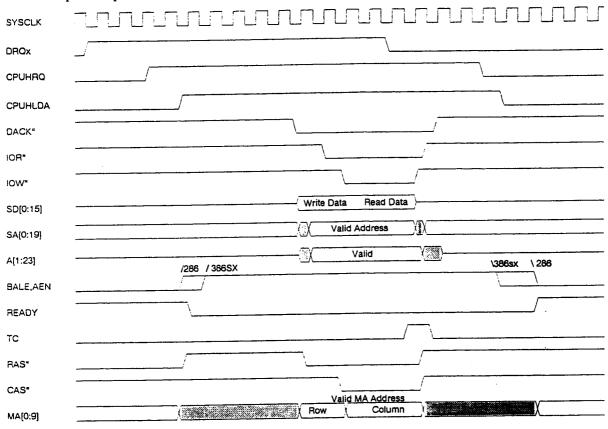

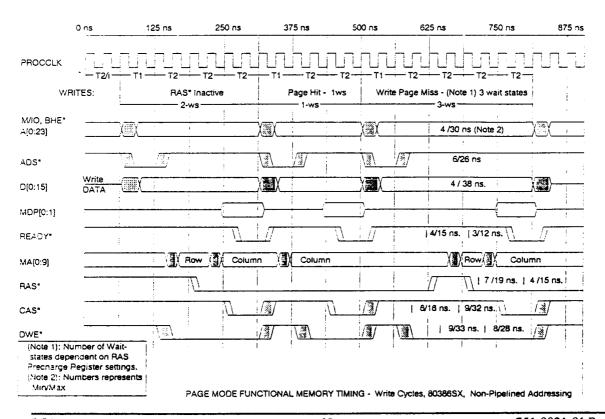

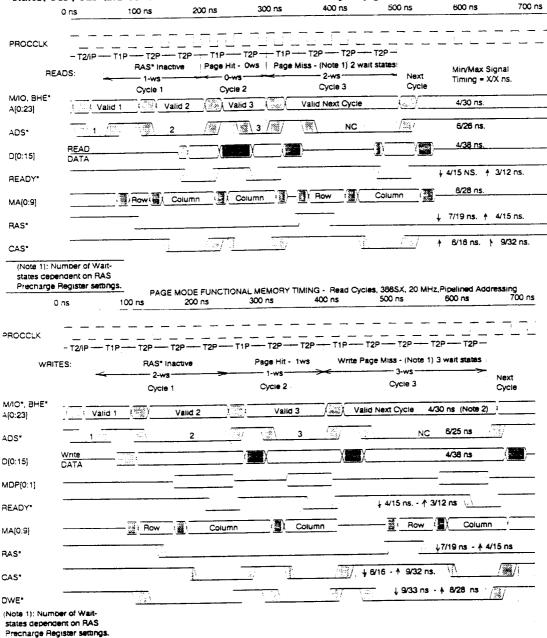

The fastest 386SX microporcessor bus cycles require only two bus states. The diagrams below show two read and write cycles with each cycle having two bus states. These bus states are named T1 and T2 or in the case of pipelined address mode, T1P and T2P.

Any memory or I/O address may be accessed by these two-state bus cycles if the responding device is fast enough. The HT21 can end these fast two-state cycles by acknowledging the end of the cycle by use of the READY\* handshake. In the event the responding device is not fast enough to complete the cycle in two-states, the HT21 delays the READY\* signal activation, causing insertion of extra bus cycles until READY\* signal activation terminates the cycle. These extra bus cycles or wait-states are further illustrated in the sections on I/O Channel Interface including: Keyboard, RTC, DMA, PIT and Interrupt Controller associated with I/O devices. The Memory Controller Section also contains explanations on wait-states during local DRAM and ROM cycles.

Pipelined address mode is required for 20MHz 386SX microprocessor operation. For this mode the NA\* signal to the HT21 and the 386SX must be tied to ground. The BHE\*, A[0:23], M/IO\* and D/C\* signals are driven low during the last T2P cycle for the next cycle. This provides the extra memory decode time needed to maintain zero wait state page operation in the upcoming cycle. The disadvantage of this mode is that in order to establish the address pipeline after an idle or hold acknowledge cycle the first cycle must be a non-pipelined T1 cycle and finish with an extra T2P cycle, as shown in the 386SX funtional CPU Pipeline Diagram.

In actual operation address pipelining is almost always maintained because in the absence of any other request, a code prefetch request is always internally pending until the instruction decoder and code prefetch queue are

completely full. This insures that when operating in this mode the address pinpeline is maintained for long periods unless the bus in not available, as in Hold Acknowledge cycles or other unusual type operations.

Detailed AC timing specifications from indicated clock edges are found in the AC Specification Section.

80386SX CPU FUNCTIONAL TIMING - Read and Write Cycles Pipelined Addressing

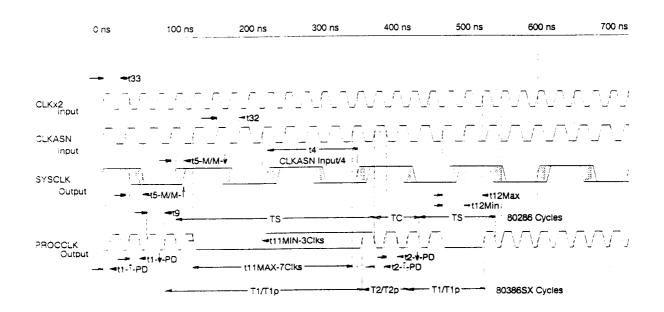

#### Clock Generation

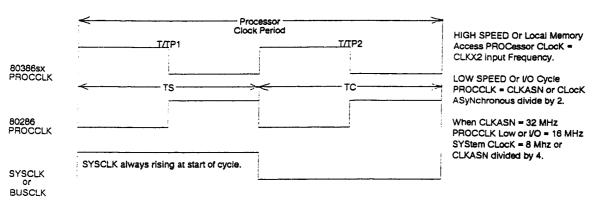

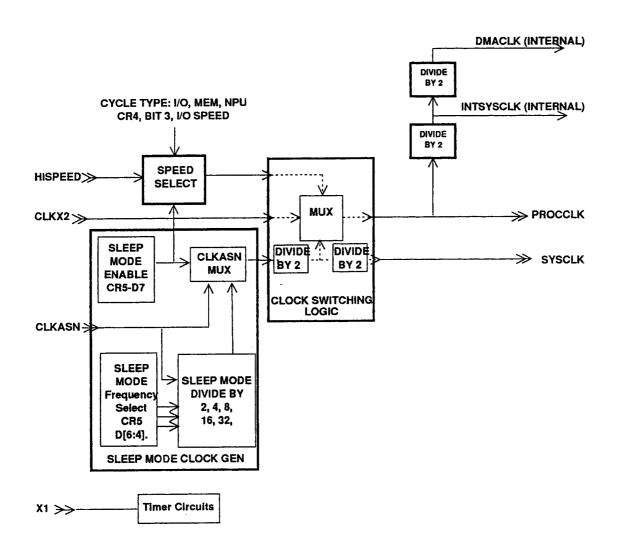

The HT21 clock generator provides all the clock switching and control for the main processor clock (PROC-CLK), power management clocks (Sleep Mode Clk), internal clocks (DMACLK), and I/O bus clock (SYSCLK). All clock signals are described below:

PROCCLK is an output clock for the selected processor and should have a frequency twice the desired processor frequency. The source for PROCCLK can switch from three sources depending on cycle type and operation mode. These three sources are CLKX2 input pin, CLKASN input pin divided by two, or the Sleep Mode Clock source.

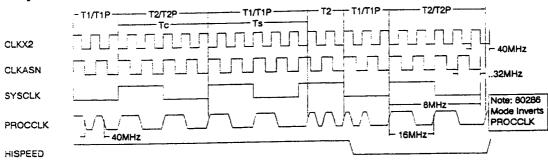

CPU PROCESSOR CLOCK RELATIONSHIPS

CLKX2 is an input pin which determines the full speed clock or the maximum CPU clock rate. The frequency of this input should be twice the desired CPU clock frequency. This input would be one of three sources used for PROCCLK.

CLKASN is an input pin that is the source for SYSCLK (system Clock), Sleep Mode Clock and an alternate PROCCLK source. The frequency of this input would be divided by two to provide the alternate PROCCLK source for low speed or special I/O operations. It is again divided by two to provide the SYSCLK (system clock) output which is typically used for system bus clock (BCLK) on an AT compatible bus. A 32 MHz input frequency is used to provide an 8 MHz SYSCLK output to meet the IEEE

P996 AT compatible bus specification and would result in a 16 MHz low speed PROCCLK frequency for an 8 MHz processor speed.

HISPEED is an input pin used to define two speed modes and is used to determine two sources of PROC-CLK. A high level on this pin would indicate the high speed mode and PROCCLK source from CLKX2. A low on this pin would indicate the low speed mode and PROCCLK source from CLKASN. In some applications this pin could be used in conjunction with 'Turbo' or high speed/low speed switch.

X1 is an input pin used to provide the clock for an internal programmable interval timer. This timer is an 8254 equivalent and can be programmed by the CPU and provides signals for system timing, refresh, and speaker tone generation.

## Internal Clocks: Clocks internal to the HT21.

DMACLK is used for internal DMA use and is the PROCCLK + 4.

## Sleep Mode - Clock Generation

SLEEP MODE operation is enabled by Control Register 5, Bit 7 which selects the Sleep Mode Clock generator as the primary system clock source, disabling the speed select logic. The frequency of this clock is selected by bits 4, 5 and 6 of Control Register 5. (See Power Management/Sleepmode Section.)

#### **CPU Clock Switching**

To maintain the highest level of compatibility with AT I/O bus specifications, while running at higher processor speeds, the HT21 allows switching between two asynchronous clock sources. A standard 20MHz CPU configuration supporting the IEEE, P996 Spec of a maximum 8MHz bus clock (SYSCLK) requires two asynchronous clock sources. The high speed CPU clock source would be a 40MHz CLock X2 (CLKX2 = CPU frequency X2). The standard 8MHz I/O bus clock or system clock (SYSCLK) and the 16MHz low speed CPU clock (for AT compatible I/O cycles) are derived from a second source CLKASN. A 32 MHz CLKASN + 4 provides an 8MHz SYSCLK and + 2 provides a 16MHz PROC-CLK during I/O cycles.

A standard 16MHz system would use a single 32MHz source for both CLKX2 and CLKASN inputs. A single 24MHz source could provide a 24MHz CPU CLKX2 and a 6MHz system clock or bus clock.

PROCCLK switching synchronization requirements will cause the last phase low period of a processor clock cycle, TS, T1, or T1P, to be extended until the clocks are synchronized. In a high speed (CLKX2 = PROCCLK source) to low speed (CLKASN = PROCCLK source) switch, the low period will be extended until the rising edge of SYSCLK. A low to high speed switch has no additional qualification requirements and will switch within one CLKASN period and one CLKX2 period.

CLOCK SWITCHING DIAGRAM PROCessor CLock - High speed CLock X 2 switch to Low speed 1/2 CLockASN Input - Low speed, 1/2 CLKASN to High speed, CLKX2 - HISPEED Switch High to Low

Clock Switching Diagram

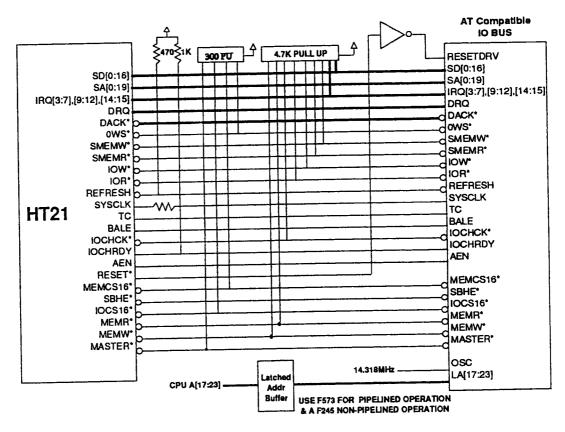

## I/O Channel Interface

The HT21 I/O Channel Interface includes all system I/O devices as well as an AT compatible 8 or 8/16 bit Bus as defined by the IEEE P996 specification. This interface is managed by an internal Peripheral Controller that is used to control all I/O channel bus cycles. From a system standpoint, these I/O channel bus cycles are defined as all CPU cycles not claimed by internal memory address decode logic and resulting CPU local bus memory cycles. This can include typical system board resources such as RTC and keyboard. These external devices are explained in detail in a separate section.

I/O Channel Interface

#### I/O Bus

The Peripheral Controller contains an I/O Bus state machine that synthesizes the address strobe signal (BALE), and many of the bus command signals (IOR\*, IOW\*, MEMR\*, and MEMW\*). It also monitors the state of the IOCS16\* and MEMCS16\* signals to determine if the device on the bus is capable of 16-bit operations for I/O and memory respectively. If a 16-bit operation is attempted with an 8-bit device, the HT21 performs the necessary conversions of 16-bit CPU operations to paired 8-bit bus cycles. Typical system implementations include an external Data bus or XD-bus that can connect 8 bit system peripherals to the CPU. The HT21 supports an external buffer connecting XD to the SD bus with an eXternal Data bus DIRection (XDDIR) output.

8/91

Basic I/O channel cycle operation occur as follows:

- 1. During processor state Ts, T1 or T1P internal decodes determine if a bus cycle should be performed.

- 2. The PROCCLK frequency is switched to CLKASN divided by 2 to provide 8MHz AT Bus compatibility. This clock switching operation may be disabled by use of the IOSPEED bit, D3, of Control Register 4.

- 3. The HT21 bus controller initiates the bus cycle by generating BALE during the I/O bus state Ts. The bus controller then times out the COMMAND DELAY interval and asserts the appropriate command output.

|                  | 1   | AT BUS<br>IEMORY<br>16-BIT | 1   | T BUS<br>I/O<br>16-BIT | AT BUS<br>INTERRUPT<br>ACKNOWLEDGE |

|------------------|-----|----------------------------|-----|------------------------|------------------------------------|

| COMMAND<br>DELAY | YES | NO                         | YES | YES                    | YES                                |

| WAIT<br>STATES   | 4   | 1                          | 4   | 1                      | -                                  |

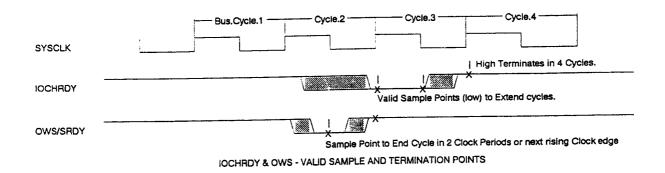

4. In response to the asserted command, the internal wait-state logic times out for the number of processor BUSCLK's before beginning to monitor the IOCHRDY input. When the IOCHRDY input sampling is active, the bus controller deactivates the command. If the cycle in process does not require conversion cycles (8-Bit to 16-Bit) the HT21 asserts READY\* and the cycle terminates. The setup time to this IOCHRDY sampling point must be maintained to properly extend the cycle.

- 5. If the cycle in progress requires a conversion cycle (8-Bit to 16-Bit), the I/O state machine sets this mode and begins to time out the BALE DELAY interval. At the end of this interval, the bus controller will be retriggered to produce another cycle as described in (3) and (4). Note that another BALE is not generated for the second cycle.

- 6. At the end of the second cycle, the HT21 generates processor READY\*, and the CPU cycle terminates.

The I/O channel clock signal, SYSCLK, is fixed at 1/4 CLKASN (unless sleep mode is enabled) but internal DMACLK and SYSCLK are always divided from the PROCCLK. See the clock generation section to understand these relationships more fully.

VO BUS FUNCTIONAL TIMING - Standard Read Cycle and Ows VO Memory Write Cycle

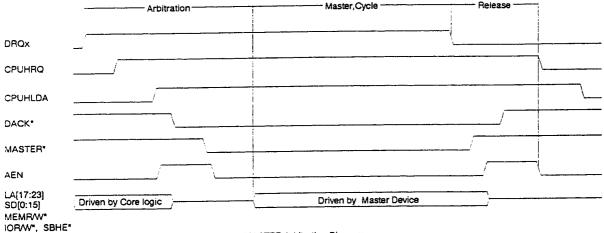

## Master Arbitration Cycle

A Master device will start the master arbitration cycle by asserting an assigned DMA Request (DRQ) and waits for the corresponding DMA Acknowledge (DACK\*) as in a standard DMA Cycle, but for correct master device operation the assigned DMA channel must be programmed for Cascade Operation. In this mode the DMA controller does not generate address or control signals and, ignores all inputs except CPUHLDA and DRQ on the active channel. When the DACK\* is received by the Master device, it will drive the MASTER\* signal. This will reverse the direction of various bus drivers and forces AEN to deassert, which indicates that the Master device has control of the bus.

The Master can remain in control indefinitely if it maintains System Refresh and can perform I/O or memory cycles as needed. In actual practice, most Master devices limit transfers to 4 or 5 cycles and then re-arbitrate by deasserting MASTER\* and DRQ. Some Master devices are able to generate very short command pulse widths in high speed, non-AT Bus compatible operations and must be set to slow or moderate speed/command pulse width timing.

The HT21 supports DMA masters on the I/O channel. A device on an I/O channel can become master and control I/O channel operations and memory access. The MASTER\* line is sampled during DMA to determine if an external bus master wishes to control the I/O channel. If the line is active, the HT21 ex-

I/O Decode

pects that the external address buffers have reversed direction. The HT21 address lines also reverse direction (they normally drive out during DMA), so the internal memory controller can obtain the address. The memory and I/O control signals also reverse while MASTER\* is active. The following diagram shows how an add-on bus master device obtains and releases control of the system.

The HT21 should retain byte swapping responsibilities with the Master device being treated as a 16-Bit resource. The Master device should not drive the SD[0:7] and SD[8:15] in a manner that would conflict with the normal byte swapping activites being performed by the HT21.

The HT21 generates MEMCS16\* or IOCS16\* internally as required for DRAM and internal register accesses, but they are not driven on the bus.

The REFRESH\* line is also bi-directional in the master environment. If the master holds the I/O channel more than 15us, it should initiate a refresh cycle. To accomplish this it should hold the REFRESH\* line active until the HT21 refresh control circuit asserts MEMR\* and brings it high again.

MASTER Arbitration Diagram

| 20 | Dec                                       | ouc |    |    |    |    |    |      |          | ADDRESS            | SELECTED      |

|----|-------------------------------------------|-----|----|----|----|----|----|------|----------|--------------------|---------------|

| Α9 | A8                                        | A7  | A6 | A5 | A4 | A3 | A2 | A1   | Α0       | RANGE(HEX)         | DEVICE        |

|    |                                           |     |    |    |    |    |    |      |          |                    |               |

| 0  | 0                                         | 0   | 0  | 0  | X  | X  | X  | X    | X        | 000 - 01F          | DMA1          |

| 0  | 0                                         | 0   | 0  | 1  | X  | X  | X  | X    | X        | 020 - 02F          | PIC1          |

| 0  | 0                                         | 0   | 1  | 0  | X  | X  | X  | X    | X        | 040 - 05F          | PTC           |

| 0  | 0                                         | 0   | 1  | 1  | 0  | X  | X  | X    | 0        | 060 - 06F          | KBC, Port B   |

| 0  | 0                                         | 0   | 1  | 1  | 1  | X  | X  | X    | X        | 070 - 07F          | RTC, NMI      |

| 0  | 0                                         | 1   | 0  | 0  | X  | X  | X  | X    | X        | 080 - 08F          | DMAPAGE       |

|    |                                           |     |    |    |    |    |    |      |          | 090 - 091          | Reserved      |

| 0  | 0                                         | 1   | 0  | 0  | 1  | 0  | 0  | 1    | 0        | 092                | SYS CTRL PORT |

|    |                                           |     |    |    |    |    |    |      |          | 093-09F            | Reserved      |

| 0  | 0                                         | 1   | 0  | 1  | X  | X  | X  | X    | X        | 0A0 - 0BF          | PIC2          |

| 0  | 0                                         | 1   | 1  | 0  | X  | X  | X  | X    | X        | 0C0 - 0DF          | DMA2          |

| 0  | 0                                         | 1   | 1  | 1  | X  | X  | X  | X    | 0        | 0F0 -              | CLR BUSYCOP   |

| 0  | 0                                         | 1   | 1  | 1  | X  | X  | X  | X    | 1        | 0F1 -              | RESETCOP 287  |

| 0  | 0                                         | 1   | 1  | 1  | X  | 1  | X  | X    | X        | 0F08-0FF           | NPCS*         |

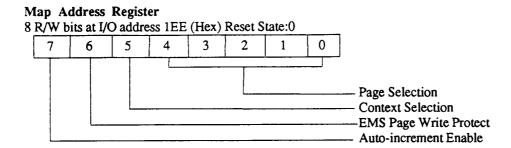

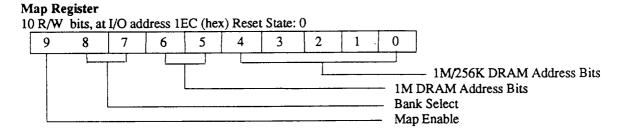

| 0  | 0                                         | 1   | 1  | 1  | 0  | 1  | 1  | X    | X        | 1EC - 1EF          | EMS/CONFIG    |

|    |                                           |     |    |    |    |    |    |      |          |                    | REGISTER      |

|    | 60-6F is KBC if A0=0, and Port B if A0=1; |     |    |    |    |    |    | 070- | 07F is F | RTC if A0=1 and NI | ∕II if A0=0   |

|    |                                           |     |    |    |    |    |    |      |          |                    |               |

## I/O Address Map

The following table defines the I/O ports supported by the HT21. Certain address locations may not be used or reserved locations. Addresses shown in numerical order.

#### I/0 TYPE

| Addr<br>Port       | Read/<br>Write        | Description                      |

|--------------------|-----------------------|----------------------------------|

| DMA Controlle      | r#1                   |                                  |

| 0000H              | R/W                   | Channel 0 current address        |

| 0001H              | R/W                   | Channel 0 current word count     |

| 0002H              | R/W                   | Channel 1 current address        |

| 0003H              | R/W                   | Channel 1 current word count     |

| 0004H              | R/W                   | Channel 2 current address        |

| 0005H              | R/W                   | Channel 2 current word count     |

| 0006H              | R/W                   | Channel 3 current address        |

| 0007H              | R/W                   | Channel 3 current word count     |

| H8000              | R/W                   | Command/Status Register          |

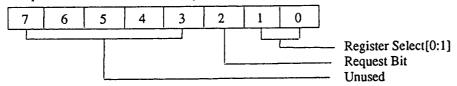

| 0009H              | R/W                   | Request Register                 |

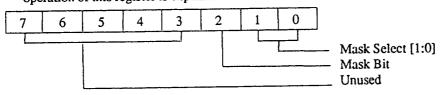

| 000AH              | R/W                   | Single Bit Mask Register         |

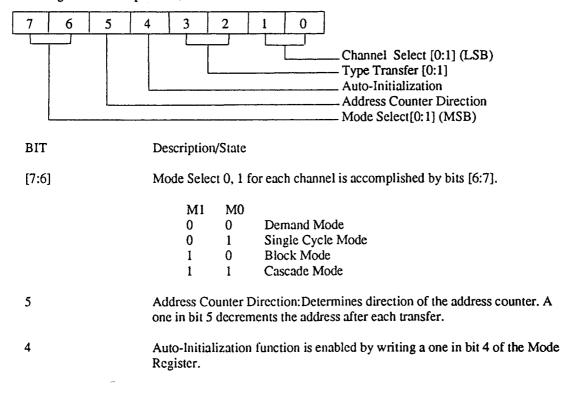

| 000BH              | R/W                   | Mode Register                    |

| 000CH              | R/W                   | Clear Byte Pointer               |

| 000DH              | R/W                   | Master Clear                     |

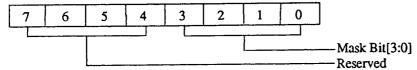

| 000EH              | R/W                   | Clear Mask Register              |